# **UNIVERSITE PARIS-SUD**

ÉCOLE DOCTORALE : STITS Laboratoire des Signaux et Systèmes

**DISCIPLINE PHYSIQUE**

# THÈSE DE DOCTORAT

soutenue le 10/12/2013

par

# Alicja MICHALOWSKA

Etude et développement d'ASIC de lecture de détecteurs matriciels en CdTe pour application spatiale en technologie sub-micrométrique

Studies and development of a readout ASIC for pixelated CdTe detectors for space applications

Directeur de thèse :Philippe FerrandoCEA-Saclay/IRFU/SApResponsable de thèse :Olivier GevinCEA-Saclay/IRFU/SEDI

Composition du jury:

Président :Jacques Olivier KLEINU-PSUD XI/IEFRapporteurs :Jean François GENATUPMC/LPNHELothar STRUDERPNSensor

Examinateurs : Michel PANDAVOINE Université Burgogne/LE12

Guillaume MONTEMONT CEA-LETI/LDET

« Experimental physics cannot be properly done without instruments. » Jean-Antoine NOLLET

# Studies and development of a readout ASIC for pixelated CdTe detectors for space-applications

« Je n'ai fait celle-ci plus longue que parce que je n'ai pas eu le loisir de la faire plus courte. » Blaise PASCAL

# **ACKNOWLEDGEMENTS**

I want to thank my wonderful supervisors Olivier Gevin and Olivier Limousin for their professional support, the numerous ideas they have shared and for their capability to identify and to show me how horizons can be reached, as well as for all the jokes and smiles they have provoked, which made this a really fun project. I am grateful to both Oliviers and to my remarkable thesis director – Philippe Ferrando, for having me involved in this very exciting project. I wish them all the best in further continuations. I am also very grateful for their proof reading of this bulky manuscript, their useful comments and advice contributed to the final shape of this thesis. In this matter I especially appreciate the detailed mathematical scrutiny of Olivier Gevin, which was extremely helpful.

Furthermore I would like to thank the following group of very special people:

To my microelectronics colleagues, especially Francis Lugiez and Eric Delagnes, for useful technical discussions as well as for making me welcome at CEA and making me part of the team.

To Sebastien Dubos, whose long days spent in the lab made it possible, that I could include the complete  $D^2R_1$  measurements results in this thesis, and to whom I also wish lots of courage for the successful continuation of the research project.

To Claire Blondel and Diana Renaud, for their patience in establishing the detector setups, the contribution of a high level of technical detail and the motivation for improving the quality of our experiments.

To Xavier Coppolani for all the lab support and for the measurements he has performed that greatly contributed to the Caterpylar characterization, and for his joyful "bonjour" at the morning coffee time.

To Remy Chipaux and François Daly for their involvement in the one-year long irradiation experiment and their readiness to meet at the Cocase facility for taking the measurement points.

And to all of my colleagues at CEA, especially from IRFU, who gave a special meaning to my work through the inspiring discussions about the challenges in the modern physics.

Finally I would like to express: my gratitude to my beloved grandparents Maria and Krystyn for the belief they had in me and their pride at each of my smallest achievements, as well as the high appreciation to my dearest Richard, for his true interest, his patience and respect for my professional plans and the support at all moments, despite the long geographical distance that stood often in between us.

All of you have some share to the work presented below.

I also thank the institutes of CEA-IRFU and CNES for co-financing this research project.

# TABLE OF CONTENTS

| ABSTRACT  |                                                             | 11 |

|-----------|-------------------------------------------------------------|----|

| 1. NEW IN | STRUMENT FOR HARD X-RAY IMAGING SPECTROSCOPY                | 13 |

| 1.1. X-ı  | RAY IMAGING TELESCOPE FOR ASTROPHYSICS                      | 14 |

| 1.1.1.    | High energy astrophysics in space, X and gamma rays         | 15 |

| 1.1.1.    | 1. Optics – Imaging techniques                              | 16 |

| 1.1.2.    | How the detector parameters contribute to telescope quality | 18 |

| 1.1.2.    | 1. Sensitivity                                              | 19 |

| 1.1.2.    | 2. Spatial resolution                                       | 20 |

| 1.1.2.    | 3. Energy measurement                                       | 22 |

| 1.1.2.    | 4. Qualifications for space environment                     | 24 |

| 1.1.2.    | 5. Cost: power and material                                 | 24 |

| 1.2. CD   | TE — A CANDIDATE FOR HARD X-RAY INSTRUMENT                  | 26 |

| 1.2.1.    | CdTe vis-à-vis other semiconductor detectors                | 26 |

| 1.2.1.    | 1. Bandgap voltage                                          | 26 |

| 1.2.1.    | 2. Photon-detector interaction                              | 27 |

| 1.2.2.    | Cadmium telluride operation characteristics                 | 28 |

| 1.2.2.    | 1. Charge transport in CdTe                                 | 29 |

| 1.2.2.    | 2. Charge loss: detector thickness vs. bias voltage         | 29 |

| 1.2.2.    | 3. Cathode side exposition to X-rays                        | 30 |

| 1.2.2.    | 4. Dark current                                             | 31 |

| 1.2.2.    | 5. Dark current reduction                                   | 32 |

| 1.2.2.    | 6. Energy resolution                                        | 34 |

| 1.2.3.    | Position sensing: strip or pixel?                           | 36 |

| 1.2.3.    | 1. Double-sided strip detector                              | 36 |

| 1.2.3.    | 2. Pixelated detector                                       | 37 |

| 1.2.4.    | Optimal pixel pitch                                         | 38 |

| 1.2.4.    | 1. Small pixel effect                                       | 38 |

| 1.2.4.    | 2. Anode readout                                            | 40 |

| 1.2.4.    | 3. Charge sharing                                           | 40 |

| 1.2.4.    | 4. Pixel size                                               | 42 |

| 1.2.5.    | State of the art CdTe based instruments for hard X-rays     | 43 |

| 1.3. Сн   | IALLENGES FOR THE READOUT ELECTRONICS                       | 46 |

| 1.3.1.    | Desired key features                                        | 46 |

| 1.3.2.    | Trend toward a hybrid detector                              | 47 |

| 1.3.3.    | High performance ASIC requested for CdTe readout            | 49 |

| 1.3.4.    | Reaching the resolution limits                              |    |

| 1.3.4.    |                                                             |    |

| 1.3.4.    |                                                             |    |

| 1.3.4.    | ,                                                           |    |

| 1.3.5.    | Radiation hardness                                          |    |

| Bibliogra            | aphy to Chapter I:                                                        | 57 |

|----------------------|---------------------------------------------------------------------------|----|

| 2. READOUT           | ELECTRONICS FOR CDTE                                                      | 61 |

| 2.1. CDTE            | DETECTOR CHARACTERISTICS VIEWED BY ELECTRONICS DESIGNER                   | 62 |

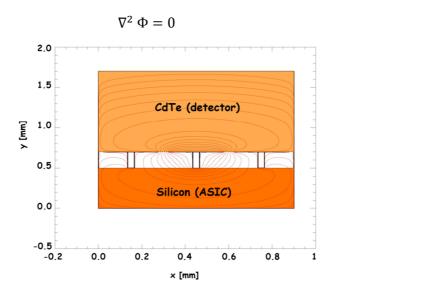

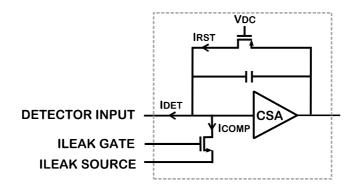

| 2.1.1.               | Electrical model of the CdTe                                              | 62 |

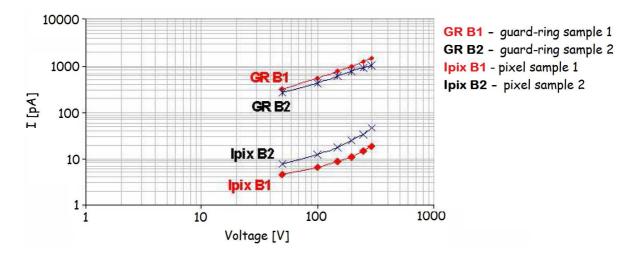

| 2.1.2.               | Expected dark current limits in the small pixel CdTe                      | 65 |

| 2.1.3.               | Expected capacitance of the small pixel CdTe                              | 67 |

| 2.1.4.               | Summary of detector parameters in the CdTe electrical model               |    |

|                      | EPT OF THE READOUT CIRCUIT                                                |    |

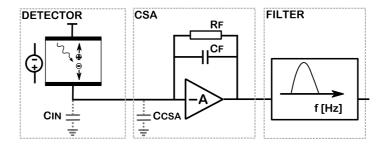

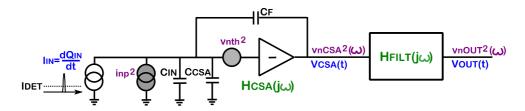

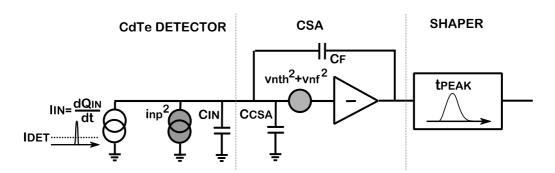

| 2.2.1.               | Three-element detection chain                                             |    |

| 2.2.2.               | Linking physics and electronics: CSA                                      |    |

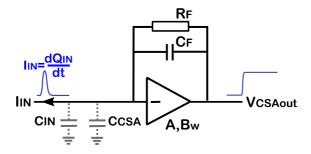

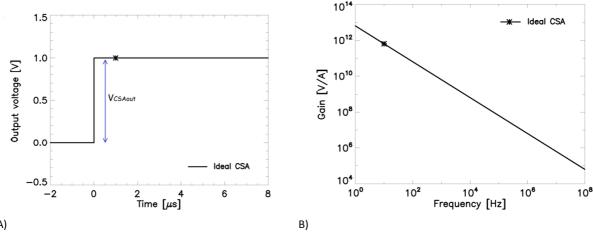

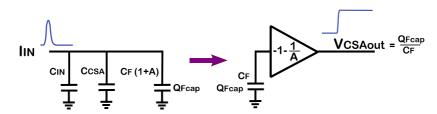

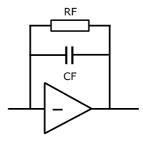

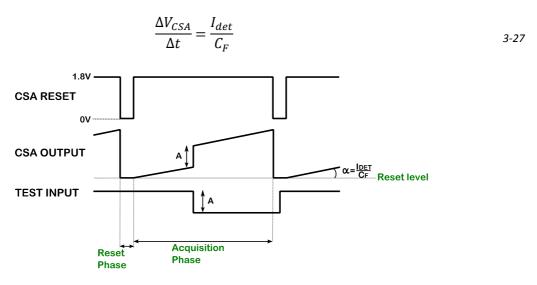

| 2.2.2.1.             | CSA operation principles                                                  |    |

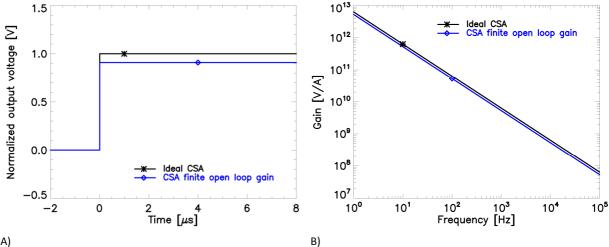

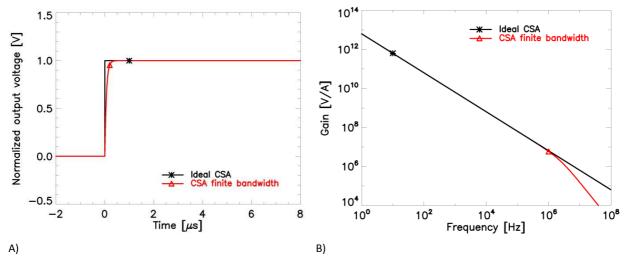

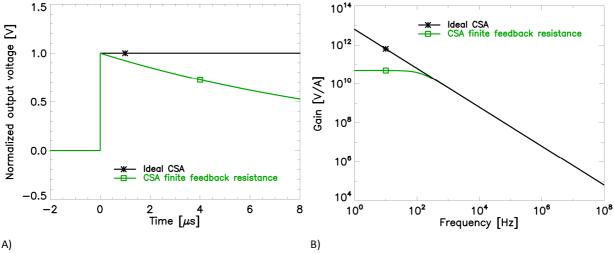

| 2.2.3.               | CSA signal and transfer function: from ideal to real                      |    |

| 2.2.3.1.             | CSA with a finite open loop gain                                          |    |

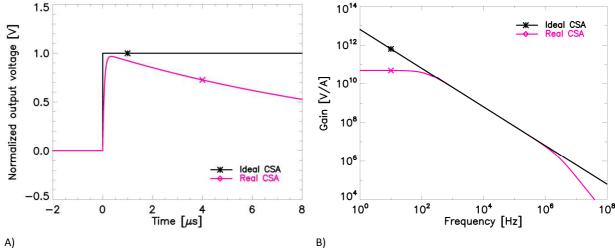

| 2.2.3.1.             | Non-zero CSA input capacitance                                            |    |

| 2.2.3.3.             | CSA with a finite bandwidth                                               |    |

| 2.2.3.4.             | Effect of the finite feedback resistance on the CSA transfer function     |    |

| 2.2.3.5.             | Real CSA                                                                  |    |

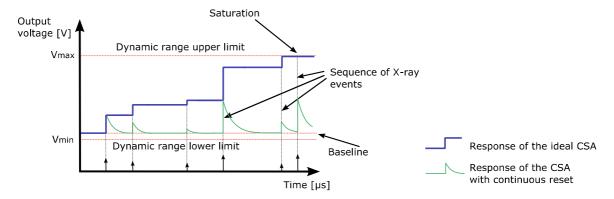

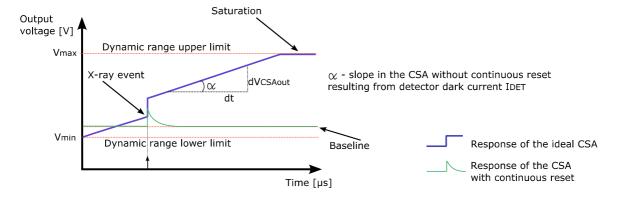

| 2.2.4.               | CSA reset circuit                                                         |    |

| 2.2.4.1.             | Feedback resistance                                                       |    |

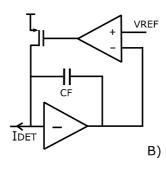

| 2.2.4.2.             | Feedback MOS transistor                                                   | _  |

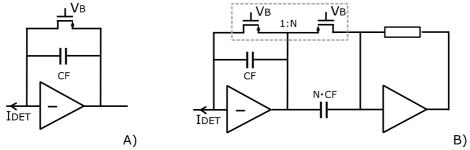

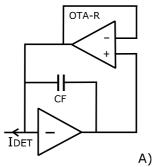

| 2.2.4.3.             | Low frequency feedback loop                                               |    |

| 2.2.4.4.             | Current conveyor                                                          |    |

| 2.2.4.5.             | Switched reset                                                            | 81 |

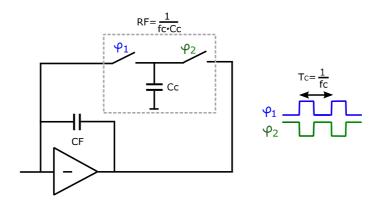

| 2.2.4.6.             | SCR – Switched Capacitor Resistance                                       | 82 |

| 2.2.4.7.             | Conclusion on reset networks                                              | 83 |

| 2.2.5.               | Presence of noise in the detection chain                                  | 84 |

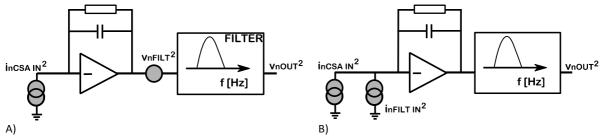

| 2.2.5.1.             | Noise amplification                                                       | 84 |

| 2.2.5.2.             | Noise sources in radiation detection chain                                | 85 |

| 2.2.5.3.             | Detector shot noise                                                       | 86 |

| 2.2.5.4.             | Detector Fano noise                                                       |    |

| 2.2.5.5.             | Thermal noise                                                             |    |

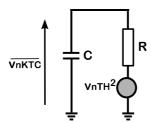

| 2.2.5.6.             | Integrated thermal noise - $kT/\mathcal{C}$ noise                         |    |

| 2.2.5.7.             | Flicker noise                                                             |    |

| 2.2.5.8.             | Dielectric noise                                                          |    |

| 2.2.5.9.             | External noise sources                                                    |    |

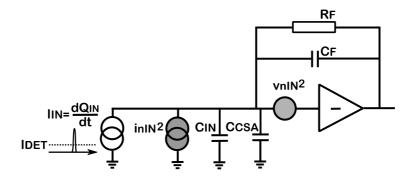

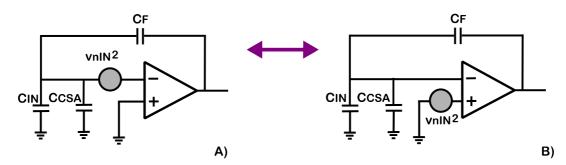

| 2.2.6.               | CSA noise transfer function                                               |    |

| 2.2.6.1.             | Noise referred to CSA input                                               |    |

| 2.2.6.2.             | Noise referred to CSA output                                              |    |

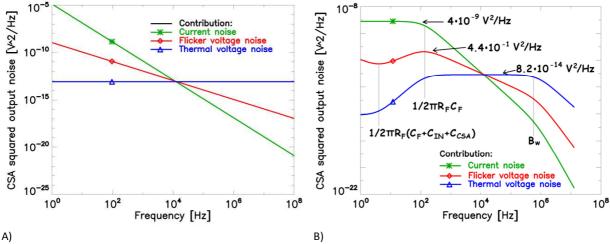

| 2.2.6.3.             | Noise power spectrum at CSA output                                        |    |

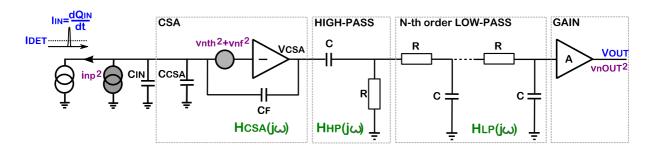

|                      | E FILTERING IN THE DETECTION CHAIN                                        |    |

| 2.3.1.               | Diversity of filters                                                      |    |

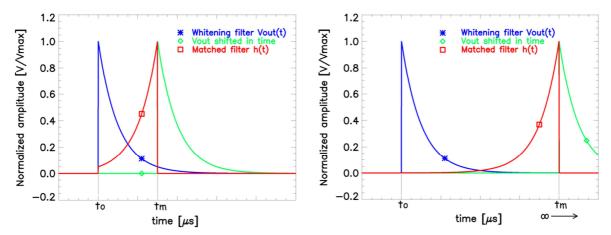

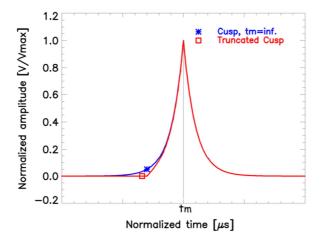

| 2.3.1.1.             | Optimal filter                                                            |    |

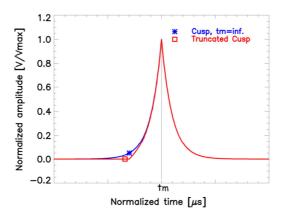

| 2.3.1.2.             | Triangular filter and other approximations of cusp                        |    |

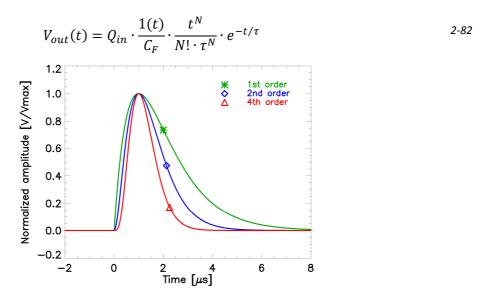

| 2.3.1.3.             | Semi-Gaussian filter                                                      |    |

| 2.3.1.4.<br>2.3.1.5. | Time invariant or time varying filters                                    |    |

| 2.3.1.5.<br>2.3.2.   | Analysis in the frequency or in the time domain                           |    |

| 2.3.2.<br>2.3.2.1.   | Frequency domain noise analysis                                           |    |

| 2.3.2.1.             | Time domain noise analysis                                                |    |

| 2.3.2.3.             | Equivalence of noise coefficients in the time and in the frequency domain |    |

| 2.3.2.4.             | Equations describing ENC                                                  |    |

| 2.3.3.               | Presentation of the optimal filter and why this chapter will continue     |    |

|                      |                                                                           |    |

| 2.3.3.1.    | ENC of the readout chain with the optimal filter              | 106 |

|-------------|---------------------------------------------------------------|-----|

| 2.3.3.2.    | Conclusions on the optimal filter                             | 107 |

| 2.3.4.      | Charms of the Semi-Gaussian shaper                            | 108 |

| 2.3.4.1.    | Filter characteristics                                        | 108 |

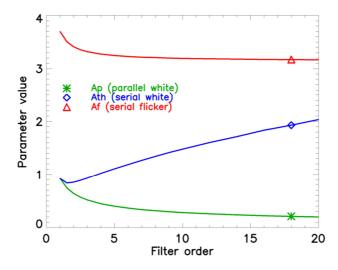

| 2.3.4.2.    | Calculation of ENC                                            | 109 |

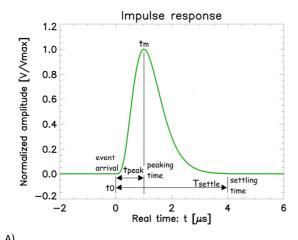

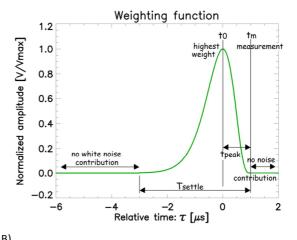

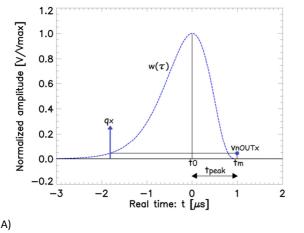

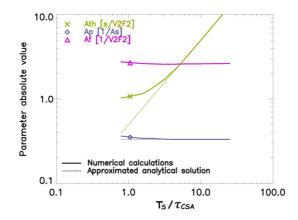

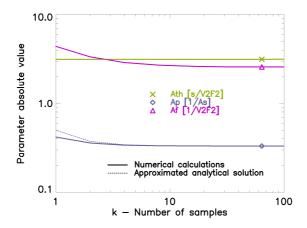

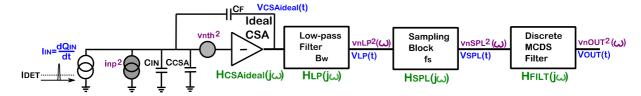

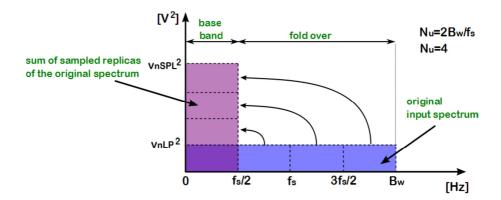

| 2.3.5.      | Deep explorations of MCDS                                     | 111 |

| 2.3.5.1.    | Properties of the correlated noise – CDS                      | 111 |

| 2.3.5.2.    | Property of averaged samples – MCDS                           | 112 |

| 2.3.5.3.    | Time domain vs. frequency domain analysis                     | 113 |

| 2.3.5.4.    | MCDS analysis in the time domain                              | 115 |

| 2.3.5.5.    | MCDS analysis in the frequency domain                         | 124 |

| 2.3.5.6.    | MCDS summary: results in the time and in the frequency domain | 129 |

| 2.3.6.      | Comparison of shapers                                         | 131 |

| Bibliogra   | aphy to Chapter II:                                           | 135 |

| 3. THE CATE | RPYLAR TESTCHIP                                               | 139 |

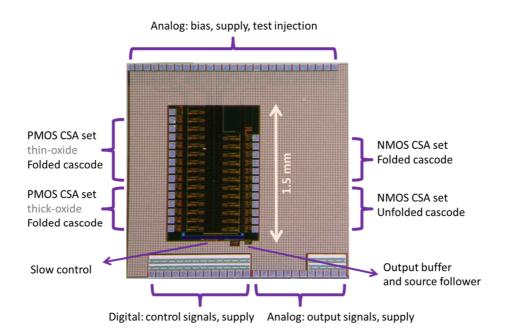

| 3.1 INTER   | EST IN THE READOUT TESTCHIP                                   | 140 |

| 3.1.1 Te    | chnology choice                                               | 140 |

|             | ne testchip goals                                             |     |

| 3.1.2.1     | IC technology validation                                      |     |

| 3.1.2.2     | CSA optimization for small pixel CdTe readout                 |     |

| 3.1.2.3     | Validation of the processing chain                            |     |

| 3.1.3 Th    | ne readout testchip input parameters                          |     |

| 3.1.3.1     | Signal polarity                                               |     |

| 3.1.3.2     | Input capacitance                                             |     |

| 3.1.3.3     | Detector dark current                                         | 143 |

| 3.1.3.4     | Energy range                                                  | 144 |

| 3.1.3.5     | Output dynamic range and feedback capacitance                 | 144 |

| 3.1.3.6     | CSA power consumption                                         | 144 |

| 3.1.3.7     | Parameters summary                                            | 145 |

| 3.2 INSIDI  | E THE CSA                                                     | 147 |

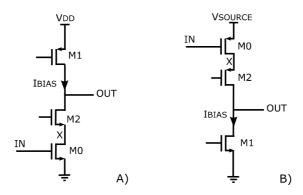

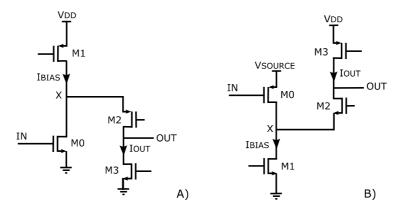

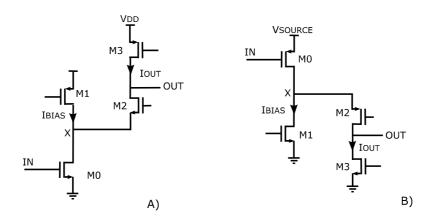

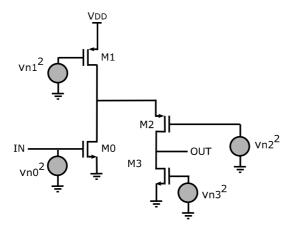

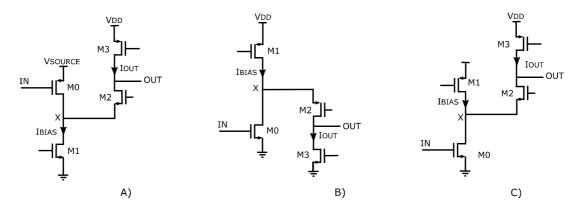

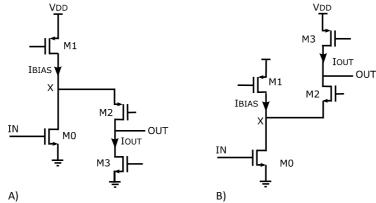

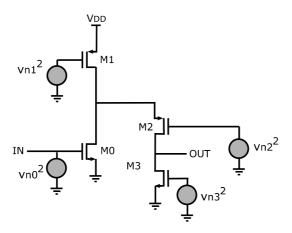

| 3.2.1 CS    | SA architectures: from simple common source to folded cascode | 147 |

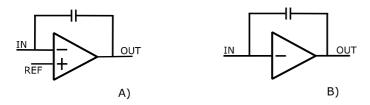

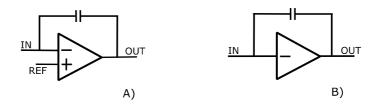

| 3.2.1.1     | Differential vs. single-ended input                           | 147 |

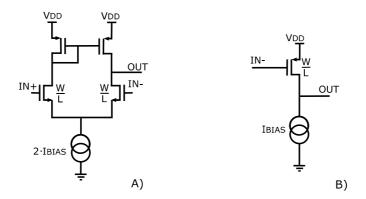

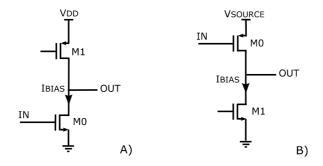

| 3.2.1.2     | Common source amplifier                                       | 149 |

| 3.2.1.3     | Telescopic cascode                                            | 150 |

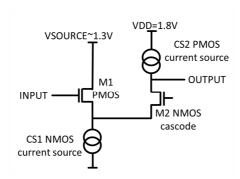

| 3.2.1.4     | Folded cascode                                                | 151 |

| 3.2.1.5     | Unfolded cascode                                              | 152 |

| 3.2.1.6     | CSA architectures summary                                     | 153 |

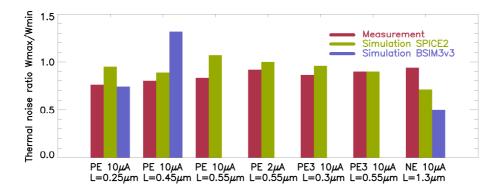

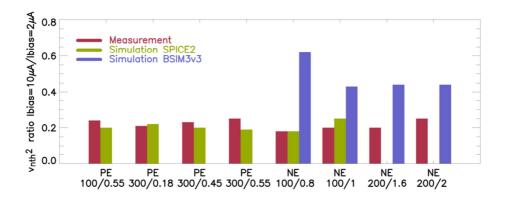

| 3.2.2 No    | oise in folded and unfolded cascode CSA                       | 154 |

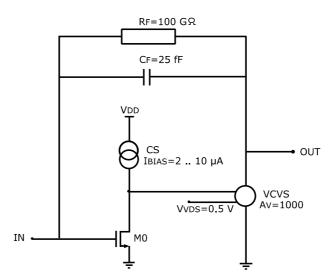

| 3.2.2.1     | Low noise CSA – design recipe                                 | 155 |

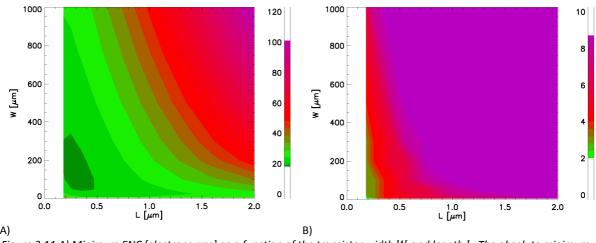

| 3.3 MULT    | TI-DIMENSIONAL OPTIMIZATION                                   | 157 |

| 3.3.1 Ca    | apacitive matching                                            | 158 |

| 3.3.1.1     | Capacitive matching – thermal noise                           | 158 |

| 3.3.1.2     | Capacitive matching – flicker noise                           | 159 |

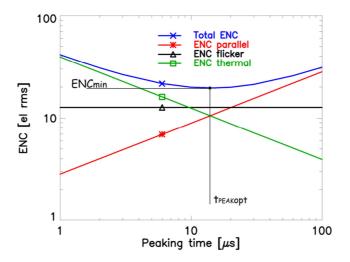

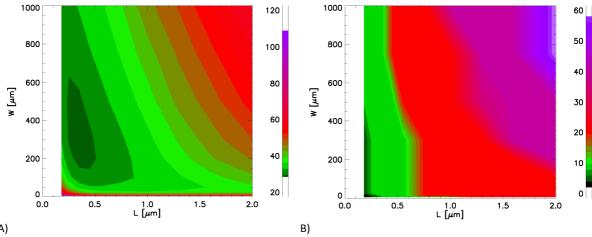

| 3.3.2 No    | umerical solution to parameterized ENC equation               | 160 |

| 3.3.2.1     | The large scale simulation                                    |     |

| 3.3.2.2     | Pseudo-ideal CSA for input transistor optimization            |     |

| 3.3.3 CS    | SA optimization summary                                       |     |

|             | nterpylar ASIC                                                |     |

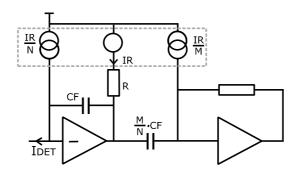

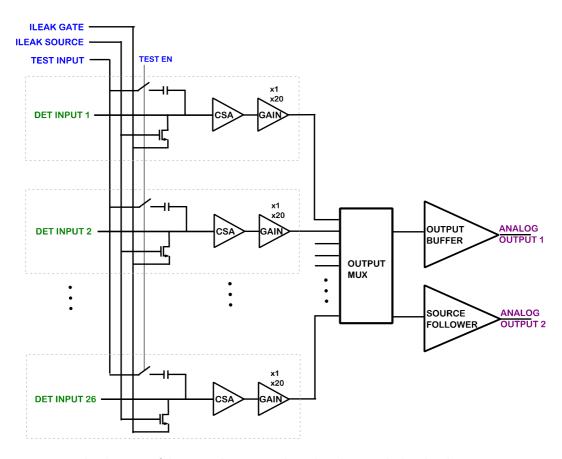

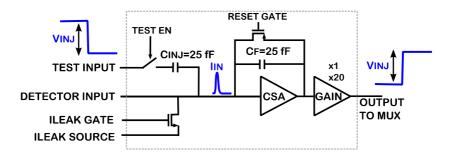

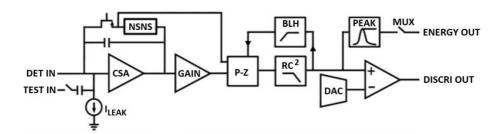

| 3.3.4.1     | Top-level circuit description                                 |     |

| 3.3.4.2     | Caterpylar three CSA architectures                            |     |

| 3.3.4.3     | Test injection                                                |     |

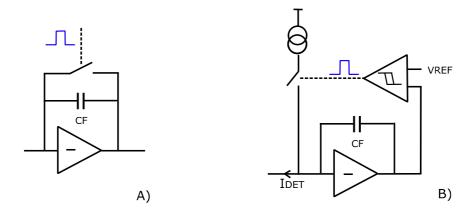

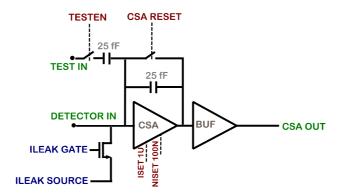

| 3.3.1.3     | CSA reset                                                     | 170 |

| 3.3.4.5     | Input current compensation                                                  | 173 |

|-------------|-----------------------------------------------------------------------------|-----|

| 3.3.4.6     | CSA buffer                                                                  | 174 |

| 3.3.4.7     | Slow Control                                                                | 174 |

| 3.3.4.8     | Caterpylar testchip summary                                                 | 175 |

| 3.4 CATE    | RPYLAR: EXPERIMENTAL RESULTS                                                | 176 |

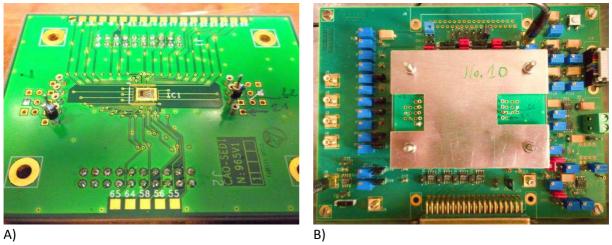

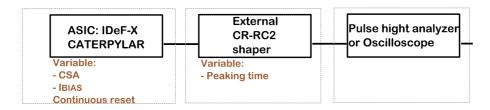

| 3.4.1 O     | verview of the measurements                                                 | 176 |

| 3.4.1.1     | Experimental setup                                                          | 176 |

| 3.4.2 F     | unctional results                                                           | 177 |

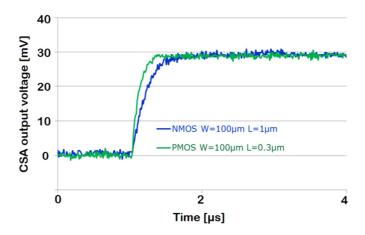

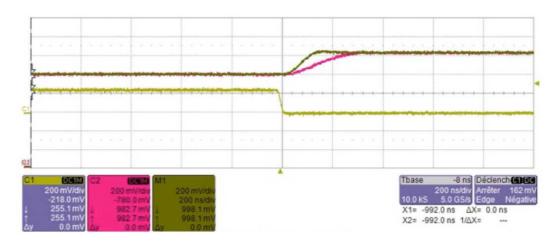

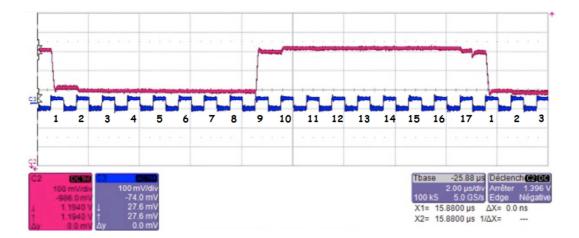

| 3.4.2.1     | Output pulse                                                                | 177 |

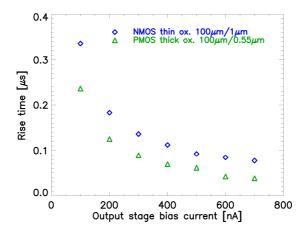

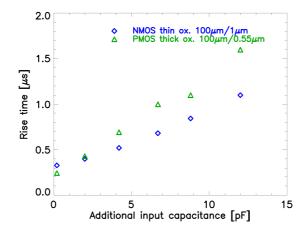

| 3.4.2.2     | Rise time                                                                   | 178 |

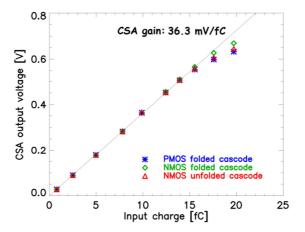

| 3.4.2.3     | Dynamic range                                                               | 180 |

| 3.4.3 E     | NC measurement                                                              | 181 |

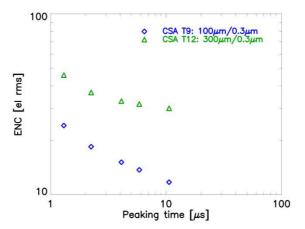

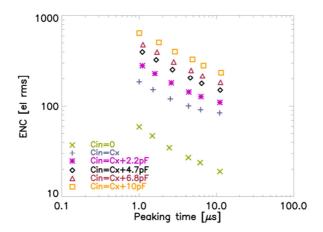

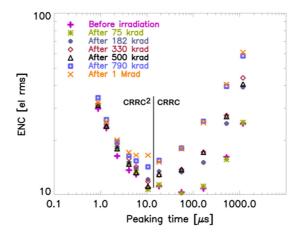

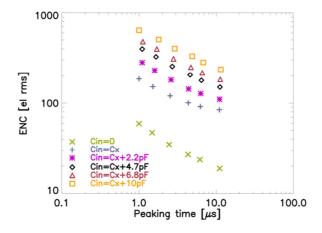

| 3.4.3.1     | ENC measurements with CR-RC <sup>2</sup>                                    | 181 |

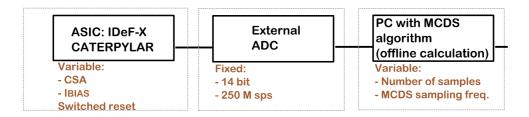

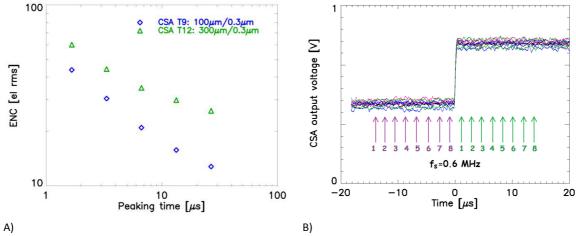

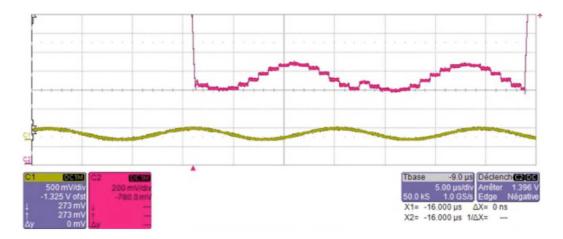

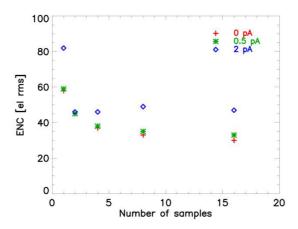

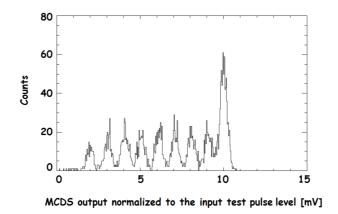

| 3.4.3.2     | ENC measurement with MCDS                                                   | 182 |

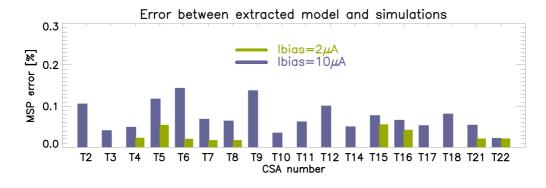

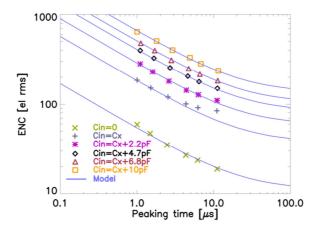

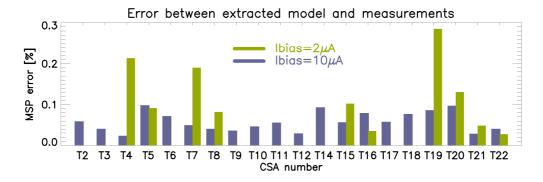

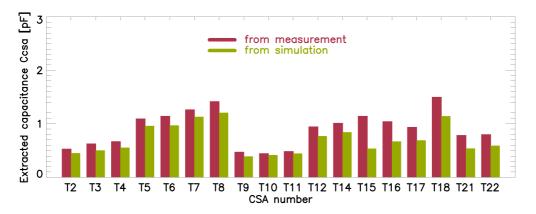

| 3.4.4 N     | Neasurements and extraction of CSA noise parameters with CR-RC <sup>2</sup> | 183 |

| 3.4.4.1     | Extraction strategy                                                         |     |

| 3.4.4.2     | Parallel noise extraction                                                   |     |

| 3.4.4.3     | Series noise extraction                                                     |     |

| 3.4.4.4     | The approach to compare ENC measurements with simulations                   |     |

| 3.4.4.5     | Studies of the extracted noise parameters                                   |     |

| 3.4.4.6     | Conclusions on extracted noise parameters                                   |     |

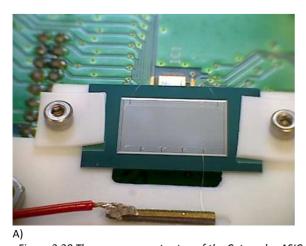

| 3.4.5 N     | Neasurements with Si detector                                               |     |

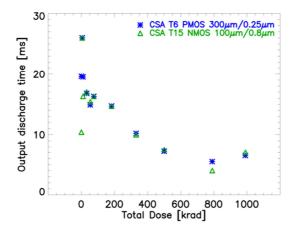

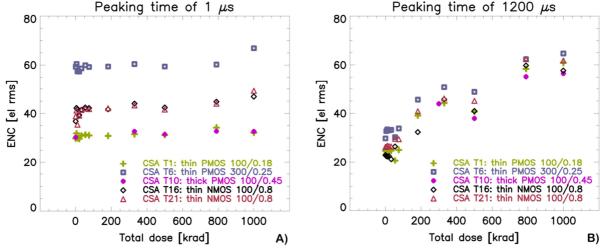

|             | otal ionizing dose tests up to 1 Mrad                                       |     |

|             | R STUDIES USING EXTRACTED <b>CSA</b> PARAMETERS                             |     |

|             |                                                                             |     |

|             | he best CSA                                                                 |     |

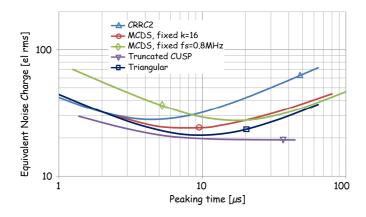

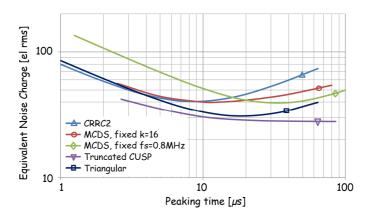

|             | chievable ENC with various filters                                          |     |

|             | onclusions on the best detection chain                                      |     |

| Bibliogr    | aphy to Chapter III:                                                        | 211 |

| 4. THE READ | DOUT ASIC D <sup>2</sup> R <sub>1</sub>                                     | 213 |

|             | -                                                                           |     |

|             | LENGES IN DESIGN CONCEPT                                                    |     |

| 4.1.1.      | Desired functionality and performance                                       |     |

| 4.1.2.      | $D^2R_1$ foundations based on experience with Caterpylar ASIC               | 215 |

| 4.1.2.1.    | CSA choice                                                                  | 215 |

| 4.1.2.2.    | Shaper                                                                      | 215 |

| 4.1.2.3.    | Reset circuit                                                               | 216 |

| 4.1.2.4.    | Technology                                                                  | 216 |

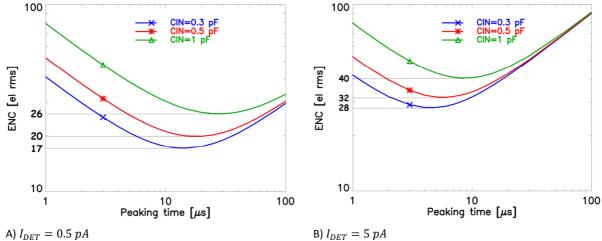

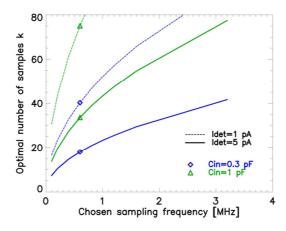

| 4.1.3.      | Shaper choice: MCDS vs. semi-Gaussian                                       | 217 |

| 4.1.3.1.    | Semi-Gaussian architecture                                                  | 217 |

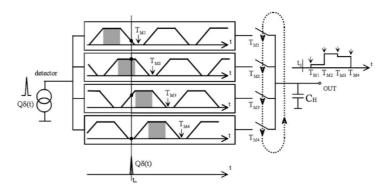

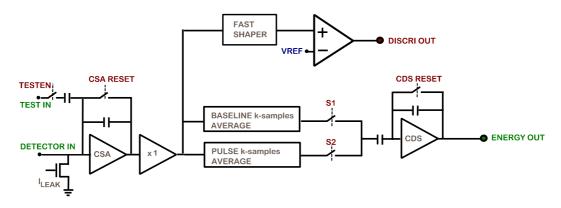

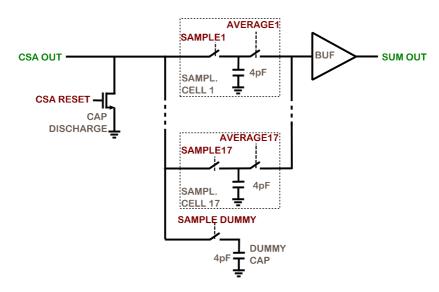

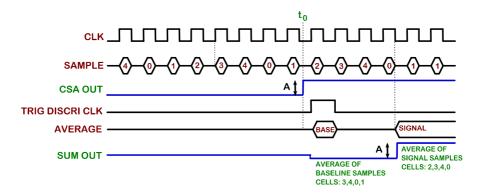

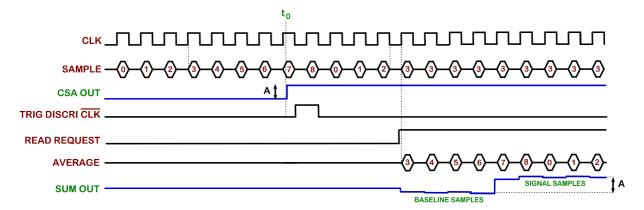

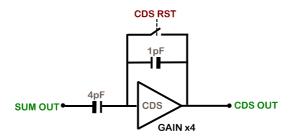

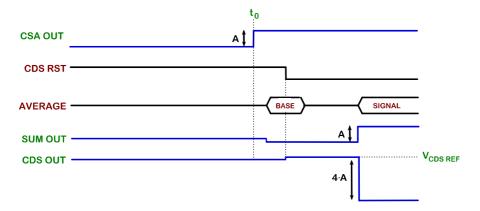

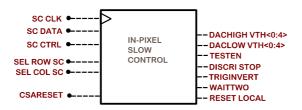

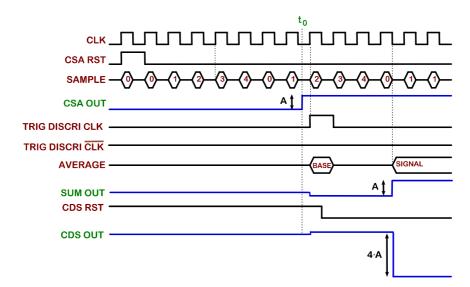

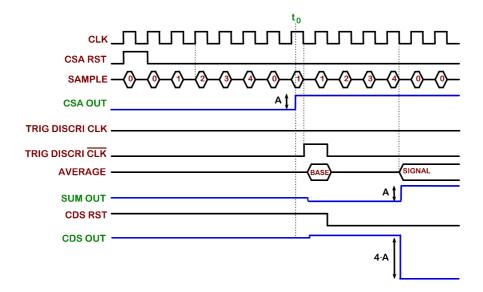

| 4.1.3.2.    | MCDS architecture                                                           | 218 |

| 4.1.3.3.    | Comparison of the two solutions                                             | 220 |

| 4.2. ASIC   | Design                                                                      | 222 |

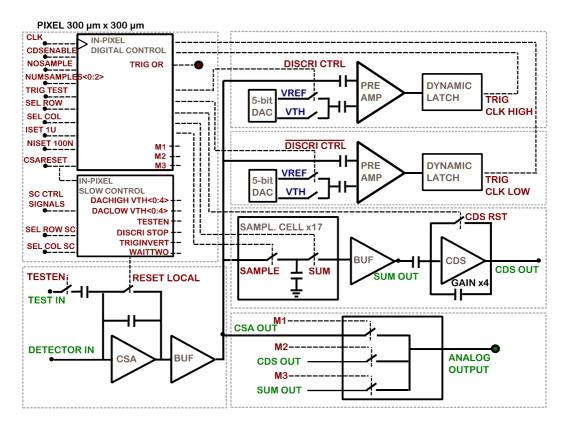

| 4.2.1.      | Pixel level                                                                 | 222 |

| 4.2.1.1.    | Top-down description of the pixel architecture                              | 222 |

| 4.2.1.2.    |                                                                             |     |

| 4.2.1.3.    |                                                                             |     |

| 4.2.1.4.    | ·                                                                           |     |

| 4.2.2.      | Top level                                                                   |     |

| 4.2.2.1.    | ·                                                                           |     |

| 4.2.2.2.    | •                                                                           |     |

| 4.2.2.3.    |                                                                             |     |

| 4.2.2.4.    |                                                                             |     |

| 4.2.2.5.    |                                                                             |     |

| 7.2.2.3.    | - P                                                                         | 233 |

| 4.      | 2.3.      | Layout and technological issues                                     | 240 |

|---------|-----------|---------------------------------------------------------------------|-----|

|         | 4.2.3.1.  | Pixel layout                                                        | 240 |

|         | 4.2.3.2.  | ASIC top-level layout                                               | 243 |

| 4.3.    | $D^2R_1$  | EXPERIMENTAL RESULTS                                                | 245 |

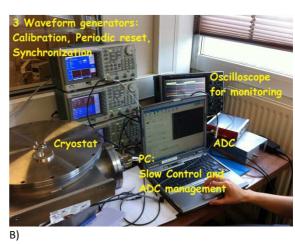

| 4.      | 3.1.      | Test environment description                                        | 245 |

|         | 4.3.1.1.  | Measurement bench                                                   | 245 |

|         | 4.3.1.2.  | Measurement setup                                                   | 246 |

| 4.      | 3.2.      | Performance                                                         | 248 |

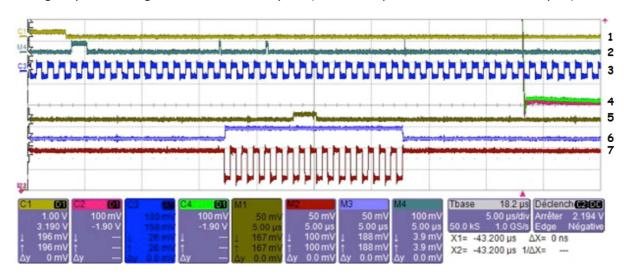

|         | 4.3.2.1.  | Functionality                                                       | 249 |

|         | 4.3.2.2.  | Gain, linearity and dynamic range                                   | 252 |

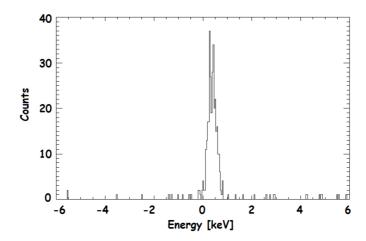

|         | 4.3.2.3.  | Measured ENC                                                        |     |

|         | 4.3.2.4.  | Low energy detection threshold                                      | 259 |

|         | 4.3.2.5.  | Power consumption                                                   |     |

|         | Bibliogra | aphy to Chapter IV:                                                 | 264 |

| 5. C    | ONCLUS    | ONS AND PERSPECTIVES                                                | 265 |

|         |           |                                                                     |     |

| 5.1.    | -         | IN THE FIELD                                                        |     |

| 5.2.    |           | N OF THE X-RAY CAMERA MODULE PROTOTYPE                              |     |

| 5.      | 2.1.      | Measurements with CdTe detector                                     |     |

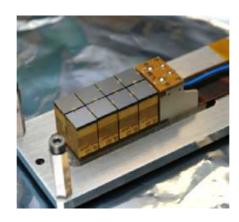

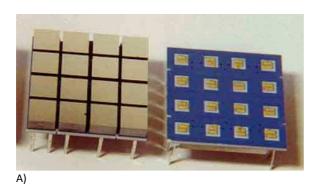

| 5.      | 2.2.      | Large detection surface                                             | 268 |

| 5.      | 2.3.      | Scaling up the ASIC                                                 | 268 |

| 5.      | 2.4.      | Space qualifications                                                | 269 |

| 5.      | 2.5.      | Emerging alternative IC technologies                                | 270 |

|         | Bibligra  | phy to Final Conclusions:                                           | 271 |

| A1.     | CALCUI    | ATION OF THE ENC WITH THE OPTIMAL FILTER: CUSP                      | 273 |

|         | The opt   | mal filter with the two-step solution                               | 273 |

|         |           | he readout chain with the optimal filter                            |     |

|         |           | nclusions on the optimal filter                                     |     |

|         | Bibliogra | aphy to Annex I:                                                    | 277 |

| A2.     | NOISE     | N THE FOLDED CASCODE CSA                                            | 279 |

|         | Bibliogra | aphy to Annex II:                                                   | 281 |

| A3.     | FULL-FI   | T NOISE MODEL TO CALCULATE ENC WITH ANY SHAPER                      | 283 |

|         | General   | description of the noise extraction                                 | 283 |

|         |           | d extraction strategy                                               |     |

| A4.     | ·         | SIS OF CATERPYLAR NOISE PARAMETERS OBTAINED WITH THE FULL-FIT MODEL |     |

| · · · · |           |                                                                     |     |

|         |           | of the extracted noise parameters                                   |     |

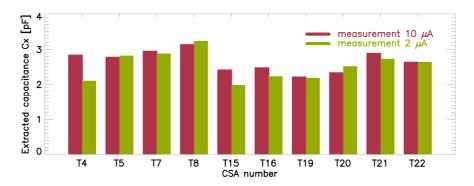

|         | •         | acitance                                                            |     |

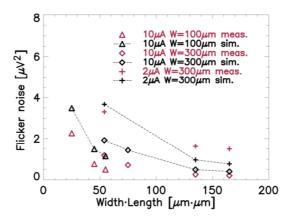

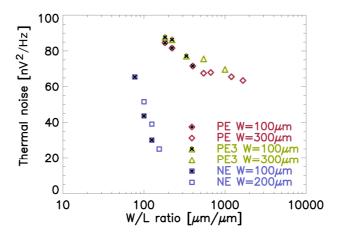

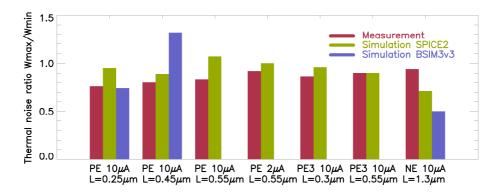

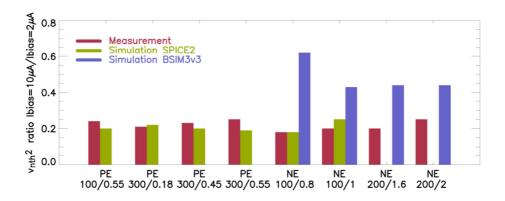

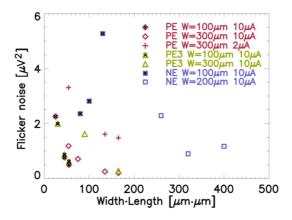

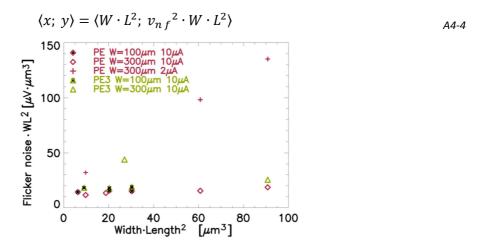

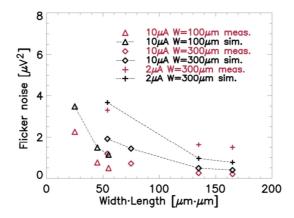

|         |           | noise                                                               |     |

|         |           | oisecapacitance <i>Cx</i>                                           |     |

|         |           | aphy fo Annex IV:                                                   |     |

|         | ואטוומום  | 7PHY TO ATTICA IV                                                   | 493 |

# **ABSTRACT**

The work presented in this thesis is part of a project where a new instrument is developed: a camera for hard X-rays imaging spectroscopy. It is dedicated to fundamental research for observations in astrophysics, at wavelengths which can only be observed using space-borne instruments. In this domain the spectroscopic accuracy as well as the imaging details are of high importance. This work has been realized at CEA/IRFU (Institut de Recherche sur les lois Fondamentales de l'Univers), which has a long-standing and successful experience in instruments for high energy physics and space physics instrumentation.

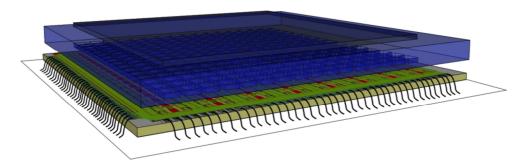

The objective of this thesis is the design of the readout electronics for a pixelated CdTe detector, suitable for a stacked assembly. The principal parameters of this integrated circuit are a very low noise for reaching a good accuracy in X-ray energy measurement, very low power consumption, a critical parameter in space-borne applications, and a small dead area for the full system combining the detector and the readout electronics. In this work I have studied the limits of these three parameters in order to optimize the circuit.

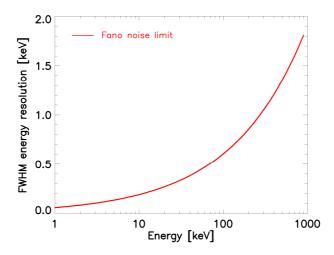

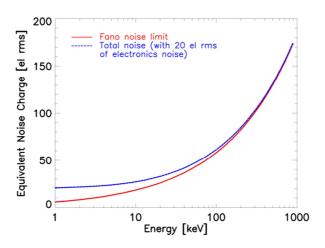

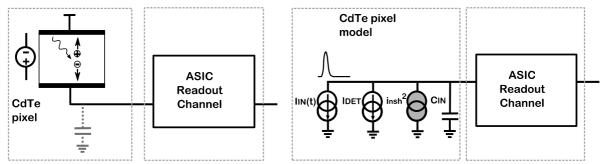

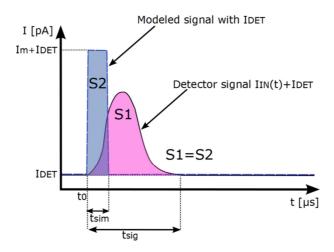

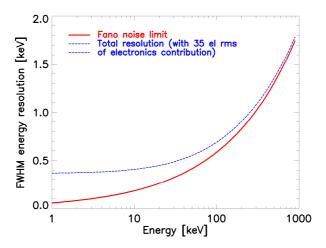

In terms of the spectral resolution, two categories of noise had to be distinguished to determine the final performance. The first is the Fano noise limit. It is the one related to detector interaction statistics and it cannot be reduced or eliminated. The second is the electronic noise, also unavoidable; however it can be minimized through optimization of the detection chain. I focused on this aspect. Within the detector, establishing a small pixel pitch of  $300~\mu m$  reduces the input capacitance and the dark current. This limits the effects of the electronic noise. Also in order to limit the input capacitance the future camera is designed as a stacked assembly of the detector with the readout ASIC. This allows to reach extremely good input parameters seen by the readout electronics, namely and input capacitance in range of 0.3~pF - 1~pF and a dark current below 5~pA.

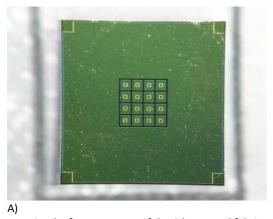

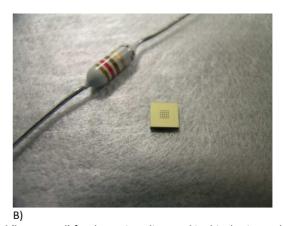

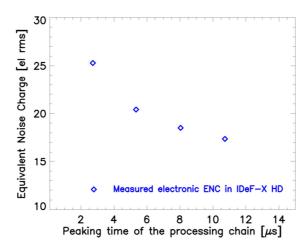

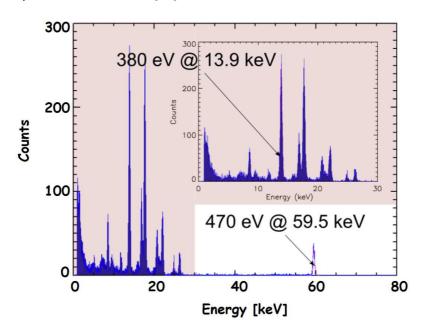

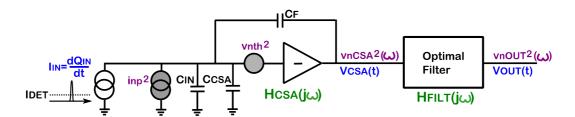

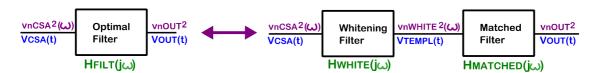

In the frame of this thesis I have designed two ASICs. The first one, Caterpylar, is a testchip, which enables the characterization of differently dimensioned CSA circuits to choose the most suitable one for the final application. It is optimized for readout of the target CdTe detector with  $300~\mu m$  pixel pitch and the corresponding input parameters. With this circuit I have also analyzed possible filtering methods, in particular the semi-Gaussian shaping and the Multi-Correlated Double Sampling (MCDS). Their comparison is preceded by the theoretical analysis of these shapers. The second ASIC D<sup>2</sup>R<sub>1</sub> is a complete readout circuit, containing 256 channels to readout CdTe detector with the same number of pixels, arranged in  $16 \times 16$  array. Each channel fits into a layout area of  $300~\mu m \times 300~\mu m$ . It is based on the MCDS processing with self-triggering capabilities. The mean electronic noise measured over all channels is 29~electrons~rms when characterized without the detector. The corresponding power consumption is  $315~\mu W/channel$ . With these results the future measurements with the detector give prospects for reaching an FWHM spectral resolution in the order of 600~eV at 60~keV.

# CHAPTER I

# New Instrument for Hard X-ray Imaging Spectroscopy

The observations in the hard X-ray domain are essential in modern astrophysics. One example is their relation to the physics of the black holes and their role in the Universe. Despite the highly penetrating properties of these high-energy photons, the thick atmosphere around the Earth absorbs the celestial flux and prevents its observation from the ground. The experiments must be carried out with instruments on satellites, in the space environment free from the atmospheric absorption. This explains why this branch of astrophysics is very young.

Another difficulty lies in the collection of the high-energy photons in hard X-ray telescopes. Because of the penetrating properties of this radiation and the very small number of photons arriving from the sources at the telescope level, this is a double challenge: for the telescope's optical system and for the detector. The optical system must provide an image of incoming photons that is then exploited further to localize the hard X-ray sources in the sky. At these wavelengths the image acquisition is realized with coded mask or focusing optics, with an image quality far from what is easily reached in the optical wavelengths detection. The detector system has to efficiently convert each of these photons, one by one, into a digital signal giving accurate position localization, the time of arrival and the energy of the incident photon. It must be realized with an extremely low intrinsic background because of the low source fluxes.

There is a list of parameters to be considered to ensure a good image quality, resolved in energy. Among them there are the position accuracy and the resolution in the energy measurement itself. To achieve good photon collection efficiency up to the hard X-ray band, an adequate detector material must be chosen. This chapter discusses why one of the most attractive materials for hard X-Ray imaging spectrometers is certainly the Cadmium Telluride (CdTe). It is a high Z and high-density semiconductor with potentially high spectroscopic performances at near room temperature. Therefore this is one of the best-suited materials for hard X-Ray space-borne applications. Once the detection material and sensor geometry are optimized, the signal from the sensor must be read out with a dedicated low noise compact electronics. Because of the number of pixels to be read out and their small size, the use of low power Application Specific Integrated Circuit (ASIC) is nowadays mandatory. In the last part of this chapter, I describe the main challenges for the readout electronics including: geometry, noise, power consumption and radiation hardness.

The electromagnetic spectrum emitted in the universe is a wide continuum ranging from radio and microwaves through infrared, visible and UV light up to the high energy X and gamma rays. The wavelengths that can be detected by astronomers range from several meters in radio band to subfemto meters corresponding to gamma rays energy of tens of TeV (Figure 1.1). Each wavelength band carries information about astronomical objects, related to their physical characteristics or to the processes developing in these objects. For example, all the recent knowledge on the origins, contents and the age of the Universe has been obtained by observations in the microwave domain, particularly by the Planck ESA mission. On the high energy side, this is in X-rays that the hot gas filling the intergalactic space in cluster of galaxies has been revealed. Through its thermal emission at temperatures of several millions of degrees one can measure the amount of dark matter in the Universe. Also this is in hard X-rays and gamma rays that the densest objects in the Universe are unveiled: neutron stars and black holes. They are both at the origin of very energetic non-thermal emission due to particles accelerated in their environment. The supermassive black holes at the center of all galaxies are now known to play a key role in the evolution, and maybe the formation, of the galaxies throughout the history of the Universe. A complete view of the Universe can be obtained only by observations in all wavelengths. Moreover in several cases this is the only way to disentangle the different theories that are competing to explain what we are observing.

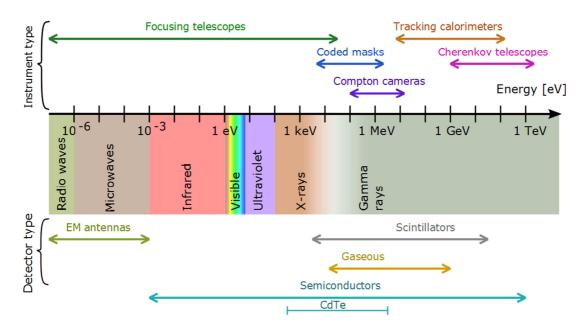

Figure 1.1 The electromagnetic spectrum with indicated characteristic bands. Instrument types used in detection for each band as well as corresponding detector types are indicated.

Investigation of each band requires a different detection method, since depending on the wavelength – the photon-matter interaction properties change. The radio and microwaves are received with antennas; light, even beyond visible, can be captured by a semiconductor-based camera. A similar principle is used for X-rays although the detector material and geometry varies with the energy range. In case of the gamma ray region – typical telescopes are based on tracking-calorimeters, Compton cameras or recently successful Cherenkov telescopes for the highest energy

range. Technological developments in the past few decades have contributed to new astronomical observations in all of these spectral domains. It is however worth noting that the Universe in far infrared as well as in X-rays has not been extensively explored, because of the limitation of the observation environment. Photons emitted within these wavelengths are completely blocked by the Earth's atmosphere. For a long time it was unknown that outside of the solar system there were astronomical sources emitting power in certain energy ranges. In the second half of the twenty-century the space environment, free from atmospheric absorption, became reachable for astrophysics experiments. The studies were then carried out with balloon-borne experiments in the upper atmosphere, rocket flights that were the initiators for X-ray sky surveys and eventually with space-borne telescopes. The latter provides the best observation conditions since in the absence of the atmosphere the detection efficiency is not restricted. Furthermore satellites can be equipped with fine pointing apparatus that prevent blurred image over long observation times. Finally duration of the mission can last up to 10 years typically, enabling an extended time for the experiment, in contrast to balloon and rocket flights – for which the observations last from few minutes up to few days at maximum.

# 1.1.1. High energy astrophysics in space, X and gamma rays

The history of X-ray astronomy starts a few decades back – in the sixties with the first discovery onboard the Aerobee rocket mission of X-rays originating from outside the solar system [1]. That event initiated this new branch in astronomy. Among the most remarkable discovery missions there were: the Einstein Observatory – the first fully imaging X-ray telescope, Chandra – with its exceptional angular resolution, XMM Newton – the largest area focusing telescope launched so far, and INTEGRAL and Fermi – covering with unprecedented performances the highest part of the spectrum, hard X-rays and MeV to tens of GeV gamma-rays. Numerous more examples could be listed all of which have contributed to the state of knowledge where we are now, in terms of astrophysics as well as detection instruments. The story continues with today's NuSTAR launched in 2012, the upcoming Astro-H, very likely SVOM, as well as well the international large projects as for example LOFT or ATHENA+ on the ESA side.

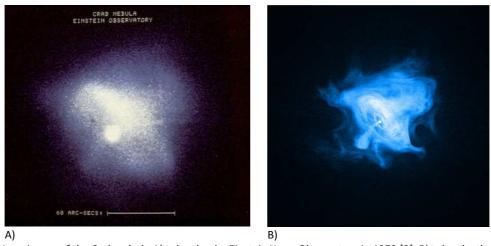

Figure 1.2 X-ray image of the Crab nebula A) taken by the Einstein X-ray Observatory in 1979 [9], B) taken by the Chandra X-ray Observatory in 2001/2004 [8].

For the last few decades the imaging devices onboard these telescopes have demonstrated a successive improvement in sensitivity and angular resolution. Fainter sources can be detected while improved spatial resolution leads to finer separation of point sources. The achievements are on one side related to better optics, and on the other side to progress in detectors development. The comparison of two X-ray images of the Crab nebula in Figure 1.2 shows an example of the impressive progress in the imaging instruments' performance over a period of 20 years.

# 1.1.1.1. Optics – Imaging techniques

In terms of optics there are two principal imaging techniques that improve the sensitivity in a given energy bandwidth, and the angular resolution, when compared to a bare detector eye: direct imaging with focusing mirror and indirect imaging with coded aperture.

#### **Grazing incidence mirror**

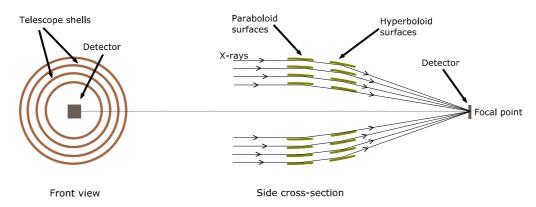

In contrast to lower wavelengths, X-rays are not reflected at all angles, but only at shallow ones. If the incidence angle is too high then the X-ray photons penetrate the matter and pass through it or get absorbed. Therefore the spherical or parabolic mirrors used for example in telescopes for visible light are not suitable for these wavelengths. The optical X-rays focus is achieved with the grazing incidence technique instead, where a beam is reflected at low grazing angles. Such a mirror can be realized using cone-like shells with multiple layers to increase the effective collecting area (Figure 1.3). Its incident curvature (combination of paraboloid and hyperboloid shells) ensures concentration of the image onto a detector area, much smaller than the telescope opening. Limitation of this method lies in the dependency between absorption incidence angle and the X-ray energy, as well as necessity to have an almost perfect mirror shape at both macroscopic and X-ray wavelength scales. This involves an excellent surface quality in order to keep the angular resolution to the requirements of modern telescopes.

Figure 1.3 Grazing incidence mirror used for X-ray focusing telescopes. The illustration includes the front view of circular shells and X-rays reflection profile in the side cross-section. A construction with multiple shells increases the effective collecting area, e.g. in the NuSTAR telescope there are 133 shells [5] and 235 shells in the future Astro-H HXT telescope [11].

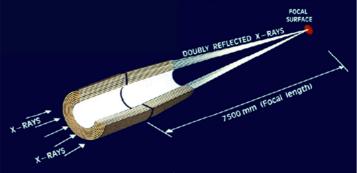

In practice the spectral window is restricted to range between a few hundreds of eV and about 100 keV. XMM Newton [6], Chandra [8] and NuSTAR [5] missions use the X-ray focusing telescope technique. The NuSTAR example demonstrates performance near the achievable upper limits of the spectral window, with energy range up to 79 keV. Figure 1.4 shows the XMM Newton satellite, with openings for the three grazing incidence mirrors. In addition the photon path through the optics to the focal surface, 7.5 meters away, is illustrated.

Figure 1.4 Image of the XMM Newton satellite [6] and illustration of its grazing incidence mirror. The energy range is from 0.1 to 10 keV and the angular resolution is 15 arcsec. This system characterizes a very good signal to noise ratio.

# **Coded mask**

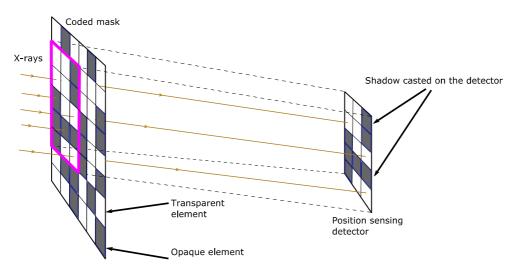

Coded mask is a different imaging technique that requires post processing to build the image. The mask is realized as a flat surface with a pseudo-random mosaic of elements that are either transparent or opaque to the photons. Typically the coded mask is larger than the detection area and placed some distance in front. Some rays pass through the mask, while others are blocked by the opaque elements casting a shadow onto the detection surface, as illustrated in Figure 1.5. The final image is obtained by unfolding the registered image from the known coded pattern of the mask. This technique is not competitive with focusing mirrors in terms of sensitivity and angular resolution. But the coded mask technique allows construction of instruments with a very large field of view, of several tens of degrees, whereas focusing telescopes are limited to a fraction of degree. This is a true advantage for all sky surveys and for the study of transient events, very important in neutron stars and black holes astrophysics. This is also the only method to cover a wide dynamic range up to the MeV region. The Integral and Swift are examples of missions using coded masks. Swift offers a very large field of view of 1.4 sr (or 4600 square degrees) [10] and can cover nearly one sixth of the sky at a time. Meanwhile the Integral IBIS instrument profits from the coded aperture technique with a very high dynamic range, which permits to observe gamma rays up to 10 MeV [2]. The Integral is shown in Figure 1.6 together with illustration of one of its coded masks used for the SPI instrument.

Figure 1.5 Illustration of the coded mask aperture imaging principle. The X-rays can pass through the transparent mask elements while they are stopped by opaque ones. In consequence a shadow is casted onto the position sensing detector. X-rays arriving from different directions result in different shadows, each of them unique. The final image is reconstructed by deconvolution of the actual detector image with the known mask pattern.

Figure 1.6 Image of the Integral satellite [3] and illustration of one of its coded masks (for the SPI instrument). The energy range is very large: from 15 keV to 10 MeV and the angular resolution is 12 arcmin. With coded mask it is difficult to achieve a signal to noise ratio as good as in the case of telescopes with focusing optics.

# 1.1.2. How the detector parameters contribute to telescope quality

The improvement in the fabrication process of grazing incidence mirrors allows their use for wider energy range and permits the construction of telescopes with extraordinarily large effective detection areas. Contemporary missions propose focusing mirrors of fine sensitivity up to energies of ~80 keV. Also coded masks can still be improved by geometry and image processing optimization. With both imaging techniques – scientific developments have led to an increase in sensitivity and angular resolution. However in addition to the optics – the observation capabilities are also associated with detector parameters. Those parameters that translate directly to sensitivity and angular resolution are the detector area, the detection efficiency, the spatial resolution in position sensing and the energy resolution as the imagers are actually spectrometers<sup>1</sup>.

|                            | Integral/IBIS [2][3]                        | SIMBOL-X [4]                             | NuSTAR [5]                   | Astro-H/HXI<br>[11][12]      |

|----------------------------|---------------------------------------------|------------------------------------------|------------------------------|------------------------------|

| Optical system             | Coded mask                                  | Grazing incidence                        | Grazing incidence            | Grazing incidence            |

| Energy range               | 15 keV - 10 MeV                             | 0.5 keV – 80 keV                         | 3 - 79 keV                   | 5 - 80 keV                   |

| Collecting area            | 2600 cm <sup>2</sup>                        | 100 cm <sup>2</sup> at 70 keV            | 60 cm <sup>2</sup> at 60 keV | 300cm <sup>2</sup> at 30 keV |

| Spectral resolution        | 9 % at 100 keV                              | < 1.3 keV at 68 keV<br>< 150 eV at 6 keV | 0.9 keV at 60 keV            | < 1 keV FWHM                 |

| Field of View<br>at 30 keV | 8.3° × 8° fully coded<br>29.1 × 29.4° total | 12'                                      | 10′                          | 9′                           |

| Angular resolution         | 12' FWHM                                    | 20" HEW                                  | 18" FWHM<br>58" HEW          | 1.7' HEW                     |

| Focal length               | 3.2 m                                       | 20 m                                     | 10 m                         | 12 m                         |

Table 1.1 Principal parameters of hard X-ray instruments onboard: the contemporary space missions – Integral (launched in 2002) and NuSTAR (launched in 2012), the future ASTRO-H (expected launch in mid-2015) as well as the SIMBOL-X (project). For IBIS, which is not a focusing instrument, the focal length is the distance from the mask to the detector. For focusing instruments, the value quoted for the Field of View is the diameter of the image at 50 % vignetting (i.e. the location off axis for which the effective area is half of the on axis effective area). For Integral IBIS, the fully coded Field of View is the one for which the collecting area (quasi-constant) is at its maximum value, the total corresponds to the angle at which the collecting area falls down to zero.

\_

<sup>&</sup>lt;sup>1</sup> I will call this type of detectors – imaging spectrometers in the rest of the text.

# 1.1.2.1. Sensitivity

One of the most important parameter of a telescope is its capacity to detect sources and to localize them over the background noise. The sensitivity of a telescope is measured in terms of a minimal flux that a source must have to be detected in a given observation time. The flux is measured in photons per unit area per second, in a given energy range. This "minimal" flux can be quantified through ratio of source signal to background noise. This Signal to Noise Ratio (SNR) is defined as:

$$SNR = S/\sqrt{S+N}$$

S being the number of counts from the source detected during the observation time, N the number of noise counts for the same observation conditions (duration, sky area, energy range). The noise considered here can have the following origins: either detection of photons and particles that are not originating from the source of interest, or detector intrinsic noise<sup>2</sup>.

#### **Collecting area**

Clearly, the signal to noise ratio always increases when the collecting area increases, whatever imaging system is considered. The larger the collecting area, the more sensitive is the telescope. Consequently the collecting surface of the telescope must be as large as possible.

In a coded mask system, the detector area is strictly proportional to the collecting area, and thus the noise is also proportional to the collecting area. A two fold increase in sensitivity can be obtained only through an increase by a factor of four of the detector area. When the coded mask aperture imaging technique is applicable (mainly in the hard X-rays and gamma rays, or in compact missions requiring a large field of view), this translates directly to large detector surfaces, typically several thousands of square centimeters. Detectors using this imaging technique, flying on INTEGRAL or SWIFT, are now at the development limit for a space borne instrument (using coded mask aperture) in terms of mass, collecting power and SNR.

In a focusing X-ray instrument, similar from the sensitivity point of view to optical telescopes, the collecting area is decoupled from the detector area. The collecting power, that is number of source counts, can be assumed to be independent from the noise counts (apart from the astrophysical noise originating from the sky itself, as e.g. the X-ray emission, at low energies, of the local bubble in which is located the solar system). The size of the mirror can be as large as feasible without increasing noise, as the photons from a point source are concentrated in a small fraction of the sensor surface (few square millimeters). For given instrument parameters (focal length and angular resolution) – the noise is constant, independently of the size of the collecting area. In consequence the background generated in the small region of the sensor where the photons are projected, is very low. Therefore the focusing X-ray telescopes provide much better sensitivity, than instruments with coded mask aperture.

#### **Detection efficiency**

In parallel to maximization of the detection area the detection efficiency also has to be maximized to improve the sensitivity of a telescope. It is described by the probability that an arriving photon interacts with the detector. As far as the hard X-rays are concerned, at energies below the pair-

<sup>&</sup>lt;sup>2</sup> In the following chapters the term "noise" will be reserved to the electronic noise.

creation threshold, there are two possible mechanisms of interaction: the photoelectric effect and the Compton Effect. The interaction probability of each process depends on the X-ray energy, detector material type and its thickness (for more details please refer to the paragraph 1.2.1). Material appropriate for detection of 6~keV X-rays may not give the same efficiency at 60~keV. In many applications not only the interaction itself is important but also it is required that the photon's entire energy is deposited within the detector. This is relevant to detectors with spectral resolution capability.

### **Observation time**

On the top of the detection area, intrinsic noise and efficiency, there is also the observation time that influences the telescope's sensitivity. With a longer exposure time a higher number of photons may be accumulated and separated from the background. For an effective observation the count rate of the instrument should match the expected luminosity of the celestial sources, typically described in number of photons per second per square centimeter. For many reasons there is only a limited exposure time given for a single observation and this is not only for the efficient use of a telescope. An object in the target image might have a transient property like gamma ray bursts or emissions from binary stars or pulsars. The observable change in these phenomena is slow enough that observation with milliseconds rate capabilities should be amply sufficient. However, a typical microsecond timing accuracy for each photon is desirable: for timing analysis of bright sources and to enable the synchronization of multiple detectors aboard.

Finally there is one more effect that may indirectly become critical for the time exposure – the emissions from beyond the desired energy band: cosmic background of high energy gamma rays or charged particles. These events also interact with the detector. The instrument responds to the resulting signal just as to any of the X-rays from the desired energy band. Such events can be rejected afterwards, however the instrument may need some time to recover until it is ready for reception of any new arriving X-rays. This dead time should be considered in the detector design, thus minimizing probability of losing any desired photon during the image acquisition time.

# 1.1.2.2. Spatial resolution

Resolving power of two celestial sources, that appear very close, depends on the spatial (angular) resolution. Having a good angular resolution is obviously also important for mapping in details extended sources, as e.g. supernova remnants which can have very thin structures. The use of imaging detectors is also needed for measuring the polarization of the radiation in hard X-rays (through the properties of the Compton interaction), a recent field under development because of the importance of this additional diagnostic for understanding the processes in the sources.

The ability to localize events is the most obvious property of imaging instruments. This can be achieved on the detector level in two ways. One possibility is a composition of multiple discrete detectors on a common detection surface. Alternatively a monolithic detector can be equipped with multiple electrodes: with one-sided pixelated or double-sided strip arrangement (for more details please refer to the paragraph 1.2.3). The total number of these segments gives the number of channels. In all cases the element in which the interaction occurs can be determined, thus providing position sensitivity with accuracy equal to separation between the elements. The parameter quality

is described by spatial  $[\mu m]$  or angular resolution [arcseconds]. For a telescope with an ideal detector the angular resolution is the minimum angle that allows distinguishing two point sources.

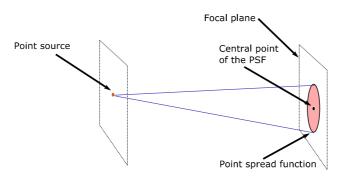

In the X-ray imaging spectroscopy the spatial resolution is given in terms of the Point Spread Function (PSF). As illustrated in Figure 1.7 – PSF is the image of a point source object projected on the focal plane.

Figure 1.7 Illustration of the Point Spread Function – describing response of an optical system to a point source object. For simplicity no focusing optics was included on the photons path.

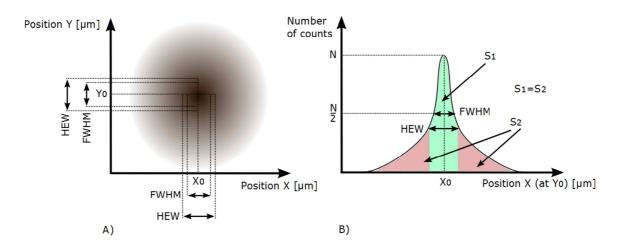

Because of the scattering effect the X-ray PSF has a particular distribution profile: narrow at the top and widened at the bottom [13]. For a first order evaluation of the angular performance of such a profile, the PSF shape is characterized either as FWHM (Full Width at Half Maximum) or as HEW (Half Energy Width):

- **FWHM**. If the maximum of the PSF corresponds to N counts, FWHM is found as the PSF width at N/2.

- **HEW** defines the PSF width where 50 % of the flux is included [14].

Figure 1.8 Illustration of the Point Spread Function parameters. A) The PSF is shown as a function of the X and Y position. The center of the PSF corresponds to coordinates  $[X_0Y_0]$ . B) The number of counts in the PSF distribution is shown as a function of the X position at the central point  $Y_0$ , with the peak of N counts. The Full Width at Half Maximum is the PSF profile width that corresponds to N/2, whereas HEW indicates width where 50% of the total flux is included (indicated with the shaded area  $S_1$  and  $S_2$ ).

Both definitions are illustrated in Figure 1.8. In X-rays imaging the FWHM term is used to describe the minimum separation of two point sources that are possible to detect, whereas HEW informs about the capability to detect faint sources [7]. FWHM and HEW, defined in Figure 1.8, are given in the unit

of micrometers and they describe the spatial resolutions. In order to describe the PSF angular resolution in arcseconds a conversion has to be considered:

$$\Theta_{optFWHM} = \frac{FWHM}{focal\ length} \cdot \frac{180}{\pi} \cdot 3600\ [arcsec]$$

1-2

$$\Theta_{optHEW} = \frac{HEW}{focal \ length} \cdot \frac{180}{\pi} \cdot 3600 \ [arcsec]$$

These equations are valid for small angles, where it can be assumed, that:  $tg(\theta) = \theta$ .

In Table 1.1 (shown at the beginning of this paragraph 1.1.2) there are listed a few space missions with their principal parameters, including the angular resolution. Observatories using coded masks, like the INTEGRAL, have the angular resolution of several of arcminutes. The NuSTAR mission [5] and the SIMBOL-X project [4], both with grazing incidence mirrors and their angular resolution (HEW) of 58 and 20 *arcsec* respectively, are excellent examples of achievable capabilities.

# Influence of detector on spatial resolution

According to the Shannon theorem in order to sample the PSF obtained for an optical system (with an ideal detector) the pixel size should be at least twice smaller than FWHM of the PSF. Thus the minimum condition between optics and detector spatial resolution is established. Ideally the detector resolution should be large enough so as not to degrade the angular resolution determined by the optical system. Therefore we must design detectors with good spatial resolution as well. In a detector of a given area, the increase in spatial resolution means an increased number of channels. For a detector with a specified pixel size, the corresponding angular resolution is defined as:

$$\Theta_{det} = \frac{pixel\ size}{focal\ length} \cdot \frac{180}{\pi} \cdot 3600\ [arcsec]$$

1-4

However there are effects related to detector physics, which will cause us to revisit the relationship for the optimal pixel size (1-4). Namely this is the charge sharing effect that degrades detector's spatial resolution. On the other hand there are processing techniques that permit to oversample the position given by geometry.

# 1.1.2.3. Energy measurement

# **Spectral resolution**

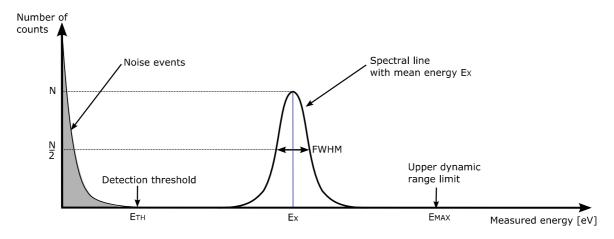

The ability to measure energy of the incoming photons is another fundamental function of an imaging instrument. The parameter known as spectral resolution is quantified in terms of Full Width at Half Maximum. Because its profile on the energy axis (Figure 1.9) is typically Gaussian (with standard deviation of  $\sigma$ ) FWHM can be calculated as:

$$FWHM = 2 \cdot \sqrt{2 \cdot \ln(2)} \cdot \sigma$$

In astrophysics the small FWHM value is important for determining the spectral emission lines, used for example in chemical composition or in red shift measurements. The energy resolution depends primarily on the type of the detector and its geometry. Furthermore the readout electronics connected to detector has significant influence on that parameter. The value of the FWHM spectral resolution usually depends on the absolute measured energy – therefore FWHM is calculated in

electronvolts at the given energy. Alternatively it is quantified in the relative unit of percent of the measured energy. Spectral resolutions of modern hard X-ray spectro-imaging instruments are shown in Table 1.1, i.e. FWHM in NuSTAR is  $0.9\ keV$  at  $60\ keV$ , whereas for the Astro-H it is envisaged to be below  $1\ keV$  over the entire energy band.

Figure 1.9 Characteristic points on a spectroscopy plot of an imaging spectrometer. The detection threshold  $E_{TH}$  has to be chosen above the intrinsic noise, no energy measurement can be achieved above the upper limit of the dynamic range  $E_{MAX}$ . A photon beam of discrete energy  $E_{\chi}$  appears in the measurement as a broader line, typically of a Gaussian shape and is described with the FWHM resolution.

# Detection threshold and dynamic range

Within the subject of the energy measurement there are two more critical parameters: the detection threshold and the dynamic range. They both define the energy band for the observation. A large energy range is desired to observe astronomical objects over a wide band. While the low energy range reveals the thermal emission of the celestial sources, the high energies are characteristics of non-thermal emissions occurring for example during particle acceleration processes. The two components are of major importance to identify the observed object nature. Most of the high-energy sources are subject to these different emission processes simultaneously, thus astronomers claim the parallel observations over wide energy band, as much as possible. There are even more arguments for that. Observation of a given type of high-energy sources in nearby galaxies or at cosmological distance will generate similar light distribution but red-shifted to the low energies. Getting a low energy band as well as a high-energy cut-off is equivalent to extend the "depth of focus" of a telescope. Besides, most of the sources, independently of their nature (black hole, neutron star, supernovae) offer much more photons at low energy than at high energy – therefore lowering the range in a high energy detector is advantageous in terms of sensitivity regarding the detection capabilities (for those sources obviously that emit at both high and low energy, which is not always the case). Using a unique instrument in these observations facilitates the cross calibrations.

The thickness of a detector will drive its detection efficiency at high energy, through the absorption probability. A relatively "large" thickness is necessary for detecting high energies, but for most techniques generates a higher background than a thin detector. Choosing the detector thickness results thus from an optimization between the efficiency and the noise level, strongly depending on the energy range of interest.

Concerning the lower energy band, in addition to the astronomer requests to detect low energy photons, low detection threshold is also useful in measurement of high energy photons. As a matter

of fact, segmented detectors, especially the pixelated ones, are subject to charge sharing between the pixels. In this case, measuring the energy in each of the pixels in which the charge is distributed is necessary for reconstructing the initial energy, by a simple sum. The lower the detection threshold, the less information is lost about the photon. Its value is mainly limited by the electronic noise of the imaging spectrometer.

For detectors, which can efficiently extend to the hard X-ray domain (above  $^{\sim}10~keV$ ) the minimum detection threshold is typically in order of few keV, as for example in case of the ASTRO-H and NuSTAR missions (Table 1.1). Concerning the upper limit, in the systems using coded masks, as the INTEGRAL — the dynamic range reaches 10~MeV. However X-ray telescopes using grazing incidence mirrors have a limited dynamic range to 70 - 80~keV, as demonstrate the examples from Table 1.1 with the SIMBOL-X, NuSTAR and Astro-H parameters.

# 1.1.2.4. Qualifications for space environment

Ability to fly in a space mission implies another group of parameters for the X-ray detector. It is related to the harsh environment for the X-rays astrophysics experiments. The shock and vibrations at the satellite launch raises requirement of solid mechanical structure. In addition, endurance as well as sensitivity to thermal environment, which may change instantaneously during the flight, must be considered in the instrument design. Once placed into orbit a satellite is exposed to all kinds of radiation from cosmic origin, both directly and indirectly through secondary particles generated into the spacecraft with intensity depending on the orbit position. This includes high-energy photons and charged particles, which not only may cause false triggers of the detector, but also far more severe consequences. The detector material is being damaged with the accumulated radiation dose, and the readout electronics can possibly experience slow degradation.

In order to guarantee a proper function of the instrument all along the space mission duration, the material and construction have to be carefully chosen. A potential detector that meets the functionality and performance requirements must undergo a series of qualification tests. The shock and vibration proofs constitute some pass conditions. There are also qualifications against damage due to radiation dose and cosmic rays effects. Finally there are life tests, which ensure a long-term operation in the harsh environment of the satellite.

# 1.1.2.5. Cost: power and material

What kind of detector type should be chosen in the X-ray astronomy experiments to meet all of the specified requirements – bulky scintillators, gaseous or semiconductor crystals? The physical dimensions are one of the cost aspects, since they often translate to the satellite payload structure mass. Compactness is one of the most important conditions that make the semiconductor detectors so popular on-board today's space-borne X-ray observatories.

The operating temperature is the second criteria in the material choice. A detector that operates in cryogenic conditions requires a complicated cooling system. This significantly increases the instrument cost: because of additional development time and – even more importantly – additional weight and complexity due to the temperature control device. This is a problem which is for example of utmost importance for detectors intended to operate in a near zero temperature. In this case the front-end electronics of the spectro-imager designed to readout the detector becomes the main

concern. For the purpose of good energy resolution this circuit should be physically placed directly next to the detector. Consequently the power dissipated by the readout electronics works against the temperature cooling (and regulating) system. This fact is important in the overall instrument design concept: the dissipated power has to be traded-off against the spatial resolution. A good spatial resolution requires a high number of detector units (pixels or strips). However the high number of channels translates to an increased power consumption in the readout electronics and more severe requirements for the temperature stabilization.

These main issues that influence the system cost, namely the material volume and the power consumption, are addressed by a careful selection of the detector type and use of integrated low power readout electronics. These two elements together constitute the core of an imaging-spectrometer instrument. In the consequent sections of this chapter I will justify the choice of the CdTe semiconductor detector, selected for the new X-ray imaging device. Secondly I will discuss requirements for the electronic circuit design: the necessary features to correctly read out information from the given detector, while meeting the criteria imposed by the astrophysicists' demands.

# 1.2. CdTe - a candidate for hard X-ray instrument

A hard X-ray imaging device can be realized in several ways. Common solutions include gaseous, semiconductor- or scintillator-based detectors. Those that are considered here are the semiconductor detectors. Typically they have significantly smaller dimensions than gas-filled instruments and a superior energy resolution when compared to indirect conversion of scintillators.

# 1.2.1. CdTe vis-à-vis other semiconductor detectors

An X-ray photon interacting in a semiconductor induces free electrical carriers. Resolution of the X-ray energy measurement increases with the number of carriers generated by the photon inside the detector. The accuracy of the energy measurement improves with a higher number of carriers. This is related to the interaction statistics. A common characteristic of semiconductor materials is a relatively low value of the ionization energy, in the order of few electronvolts per electron-hole pair. This results in a high number of carriers due to an X-ray interaction, significantly higher than e.g. in gases. In fact semiconductors offer the best intrinsic energy resolution among all types of detectors [15]. Materials belonging to this family differ from each other with certain properties. Each of the available semiconductor-based detectors has its own advantages and drawbacks, which have to be compromised to fit the application.

| Material:                         | Si   | Ge   | CdTe  |

|-----------------------------------|------|------|-------|

| Atomic number                     | 14   | 32   | 48/52 |

| Density [g/cm <sup>3</sup> ]      | 2.33 | 5.33 | 5.85  |

| Bandgap [eV]                      | 1.12 | 0.72 | 1.44  |

| Ionization energy [eV/e⁻–h⁺ pair] | 3.61 | 2.98 | 4.42  |

Table 1.2 Comparison of semiconductor properties [15][17]

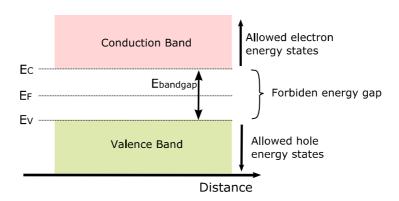

# 1.2.1.1. Bandgap voltage

The implied characteristic of all semiconductors is the presence of the bandgap between the conduction and the valence band. Its value is strongly related to the electron-hole pair creation energy. In a low bandgap material an interacting photon generates a higher number of free charge carriers, than when the bandgap is high. Consequently a better accuracy in the energy measurement can be achieved. With this respect germanium detectors are the most valuable (Table 1.2). However the low bandgap also results in higher probability of thermal excitation of an electron-hole pair, which is independent of any X-ray event arrival. The thermally generated carriers are the cause of the dark current in the detector. This effect degrades the energy resolution. The dark current has an exponential dependency on the temperature. With the compromise between the pair creation energy and the dark current a good energy resolution for germanium is achieved only in cryogenic conditions. Unfortunately a cryogenic cooling in an astrophysics instrument significantly increases the overall cost and reduces the potential lifetime of the space mission. In contrast to germanium, in silicon the operation near room temperature is sufficient to achieve a good spectral resolution below 1 % FWHM (in the energy range of up to few keV typically measured with silicon). An only slightly

higher bandgap value is observed in Cadmium Telluride, which is also suitable for operation at room temperature.

# 1.2.1.2. Photon-detector interaction

At the energies corresponding to hard X-rays the probability of an interaction between the photon and the detector also becomes an important issue, because of the important penetration capability of X-rays. In materials with higher atomic number and density, the photon absorption length is smaller. Therefore such semiconductors can provide good detection efficiency for a reasonable thickness. Cadmium telluride has the atomic number and the density significantly higher than Si, as shown in Table 1.2. Meanwhile their bandgap energy values are similar. This makes CdTe an interesting candidate for the X-ray detection.

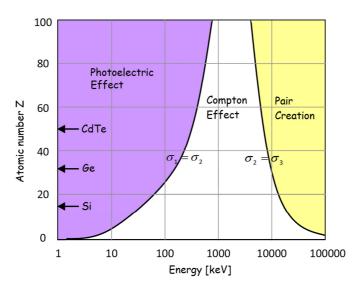

Figure 1.10 Dominating interaction effect (photoelectric, Compton and pair creation) as a function of the incident photon energy and the atomic number of the detector material [16].

There are three dominating interaction mechanisms: photo-electric effect, Compton scattering and pair production. Their respective predominance on the photon energy and on the detector atomic number is illustrated in Figure 1.10.

- Photoelectric effect is the dominant process of interaction for low energy X-rays. During the interaction between a photon with an atom the photon is completely absorbed and a photoelectron is freed from the atom. Its kinetic energy is equal to that of the photon reduced by the binding energy between the atom and the electron. The electron undergoes further interactions. In consequence the entire energy of the primary photon is absorbed locally in the detector [15].

- Compton effect. With higher energy of the incident photon, the probability of the Compton effect increases. An incident X-ray hitting the detector is scattered from an electron within an atom. As a consequence the initial trajectory of the photon is diverted by an angle φ. Meanwhile the electron is recoiled from its rest position. The energy of the secondary X-ray is given by the equation [15]:

$$E_{scatter} = \frac{E_{initial}}{1 + \frac{E_{initial} \cdot [1 - \cos(\phi)]}{m_e c^2}}$$

1-6

Where  $m_ec^2$  is the electron rest-mass equal to  $511\,keV$ . The scattered photon can escape the detector. Thus the energy of the initial incident X-ray often cannot be measured. Meanwhile the electron energy is typically absorbed resulting in a Compton background on the spectroscopic image.

• **Pair production.** Finally at high energies the result of interaction can be the production of an electron-positron pair [15]. This effect can occur if the energy of the photon is higher than 1.02 *MeV*, which is twice the electron rest-mass energy. In practice this effect occurs at energies significantly higher than that – at few *MeV*, corresponding to gamma-rays. Only special detectors with a very large volume can fully absorb the initial photon energy.

The most desirable interaction mechanism for a photon energy measurement is the photoelectric effect, where the energy is usually absorbed completely and locally. In case of the Compton and the pair-production effects – the secondary interaction product is likely to escape the detector, with only fraction of the initial energy being deposited. In Figure 1.10 the three interaction mechanisms are analyzed as a function of the photon energy and the atomic number of the detector material. From this plot it can be determined which detectors ensure that photoelectric effect dominates in the energy band of interest. In the hard X-ray domain, where the energies reach few hundreds keV, its occurrence probability is much higher with CdTe than with Si or Ge. This is a result of the high atomic number of CdTe. The photoelectric effect domination becomes the most important motivation to choose the CdTe semiconductor for photon energies measurement in the hard X-ray band.

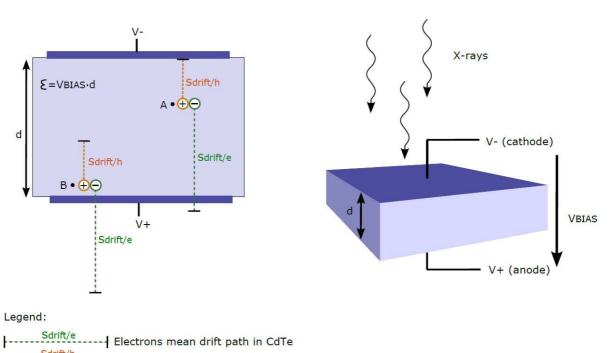

# 1.2.2. Cadmium telluride operation characteristics

A typical size of commercially available CdTe crystals is up to  $1\ cm^2$  of surface area with a thickness d in the range from  $0.5\ mm$  to a few millimeters. Each side of the detector is equipped with one or multiple metal electrodes. Like in other semiconductor detectors the X-ray interaction with CdTe results in a cloud of electrical carriers. The number of the electron-hole pairs is given by:

$$N = \frac{photon\ energy}{ionization\ energy} = \frac{E}{w}$$

1-7

| Parameter           | Symbol  | Unit                | Value in CdTe |

|---------------------|---------|---------------------|---------------|

| Electrons mobility  | $\mu_e$ | cm <sup>2</sup> /Vs | 950           |

| Holes mobility      | $\mu_h$ | cm <sup>2</sup> /Vs | 80            |

| Electrons life time | $	au_e$ | μς                  | 1.2           |

| Holes life time     | $	au_h$ | μς                  | 4.6           |

| Fano factor         | F       | _                   | 0.15          |

Table 1.3 Physical properties of CdTe [17][21]

The amount of free charge is linearly proportional to the energy of the incoming photon. In order to collect the charge on the detector electrodes a bias voltage V has to be applied. Finally the information carried by the electrical carriers is read out by an electronic circuit connected to the

detector electrodes. In CdTe the electric field  $\mathcal{E}$  applied across its volume of length d is in the order of a few hundred volts per millimeter.

$$\mathcal{E} = V/d$$

In a large electric field the free charge can be transported between the interaction point and the detector electrodes in a shorter time. This is required to provide good charge collection capability.

# 1.2.2.1. Charge transport in CdTe

Free holes and electrons in a semiconductor are characterized by two parameters related to their transport: mobility  $\mu$  and lifetime  $\tau$ . The acceleration of charge carriers due to the electric field  $\epsilon$  is disturbed by successive collisions with the semiconductor lattice. Consequently the charges move with an average velocity limited by the rate of collisions. This average drift velocity is a product of carrier mobility  $\mu$  and the applied electric field  $\epsilon$  [18].

$$v_{drift} = \mu \cdot \varepsilon$$

The second mentioned parameter, the lifetime  $\tau$ , is the average time that an electric carrier remains in free motion. In reality it may meet an impurity trap or a crystal defect where it recombines before reaching the detector electrode. A long life time and high mobility are both favorable for a good charge transport. Therefore we often speak about the products of mobility and lifetime:  $\mu_e \tau_e$  for electrons and  $\mu_h \tau_h$  for holes [15]. Unfortunately the parameters:  $\mu$  and  $\tau$  in CdTe (Table 1.3) are significantly smaller than in Si or Ge. Due to high density of the material, both holes and electrons have very low mobility. Crystal defects, even in a high purity CdTe, are manifested with relatively short life times.

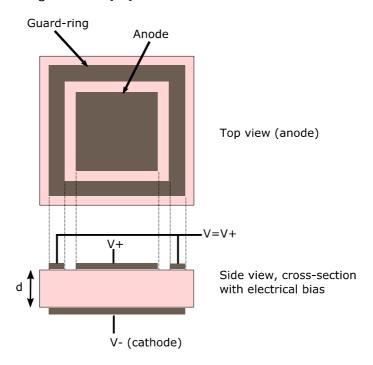

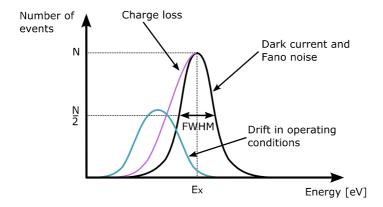

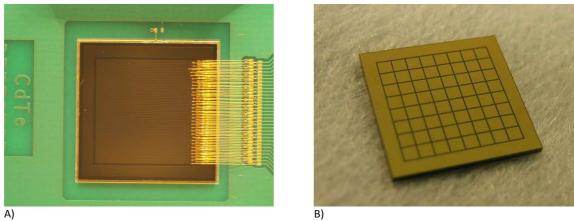

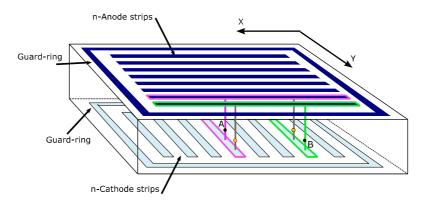

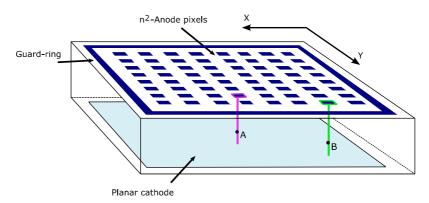

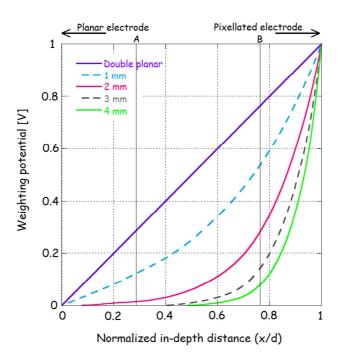

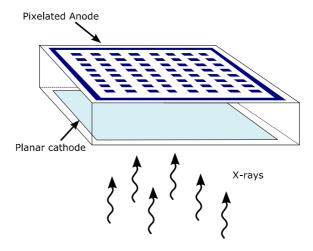

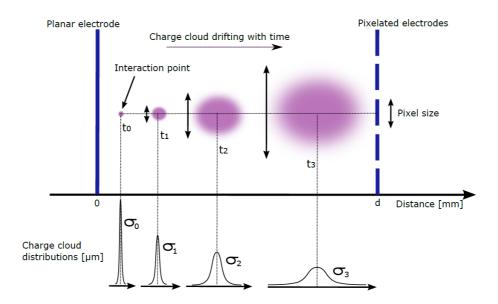

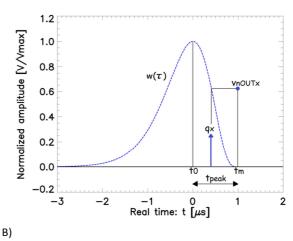

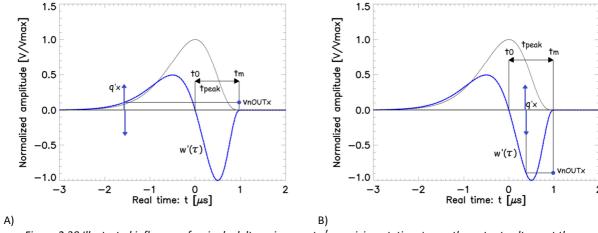

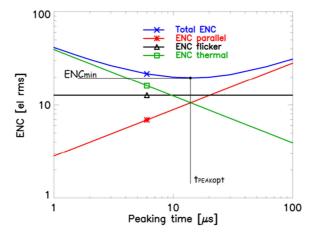

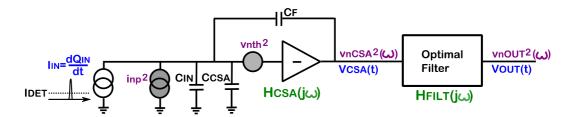

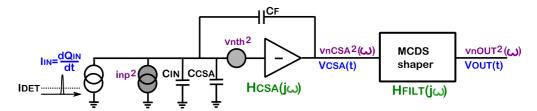

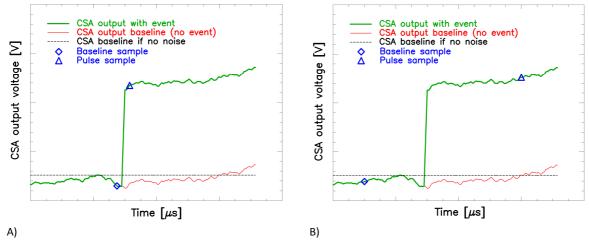

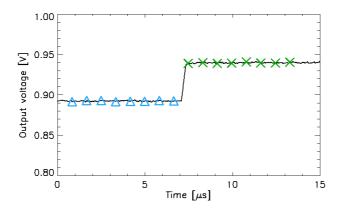

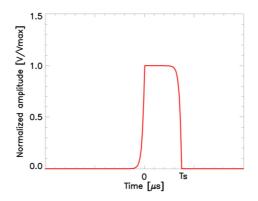

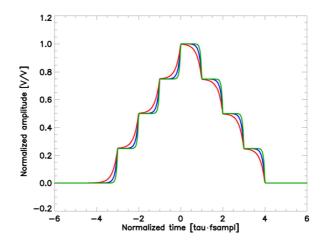

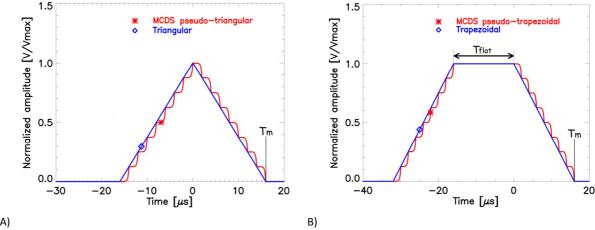

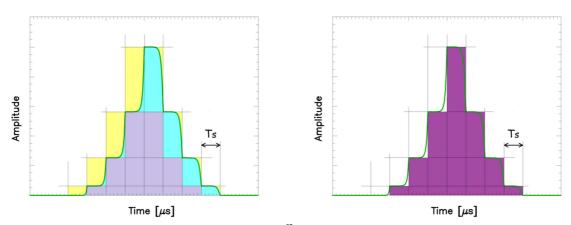

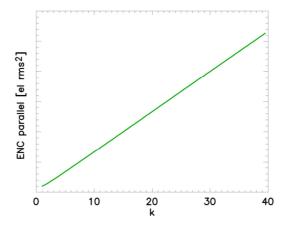

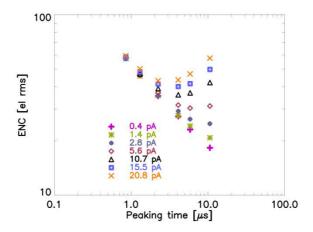

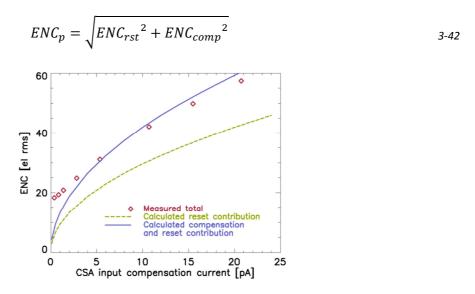

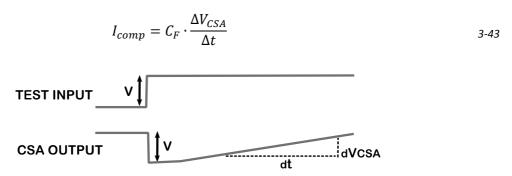

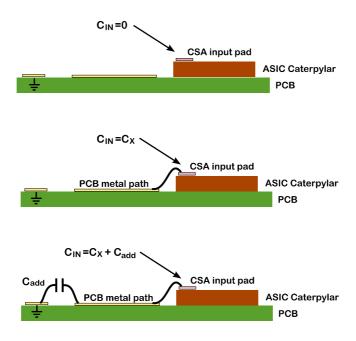

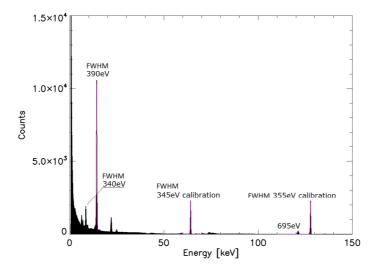

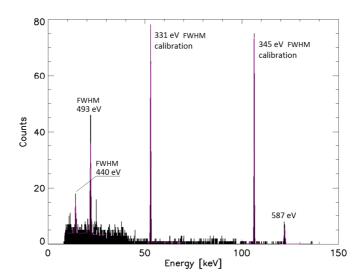

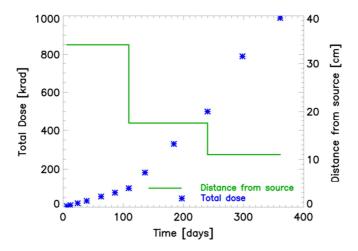

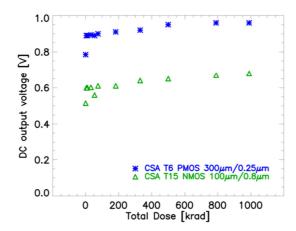

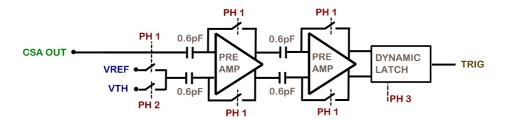

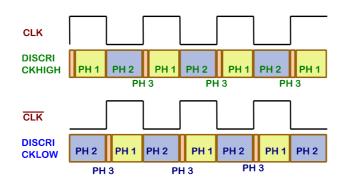

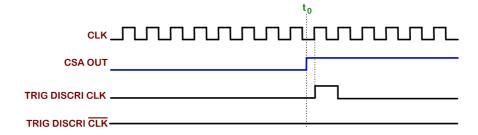

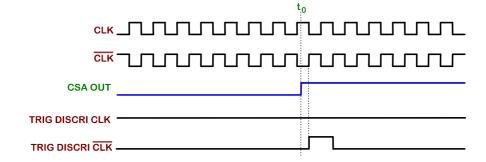

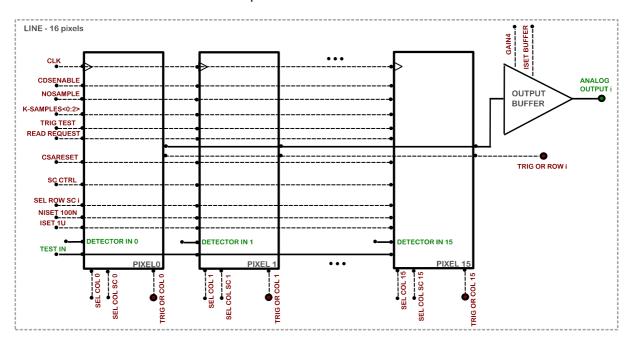

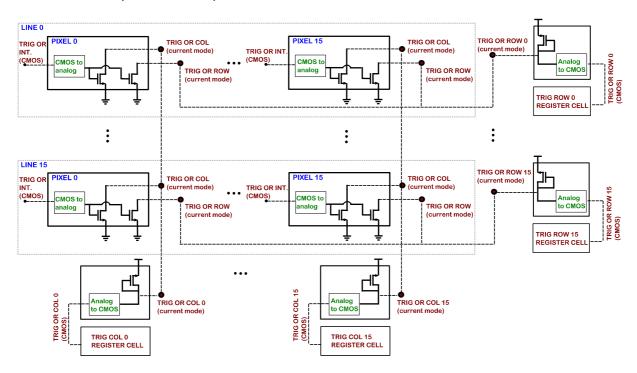

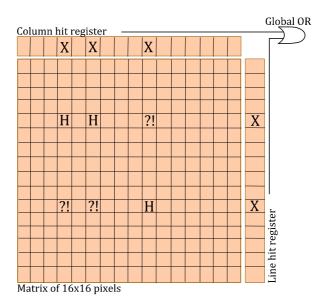

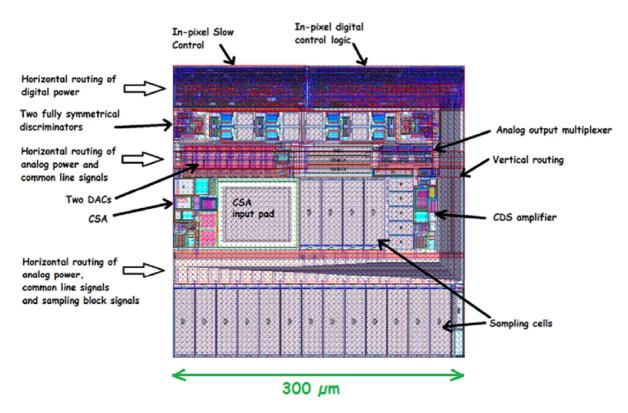

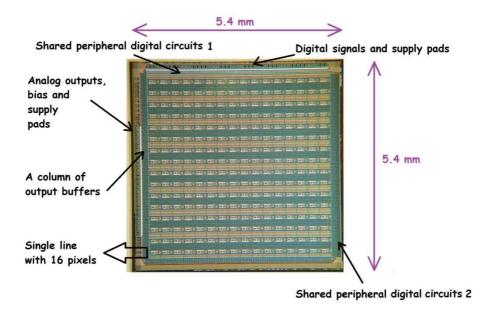

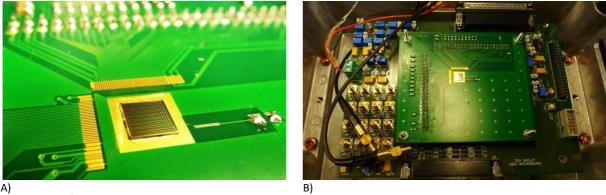

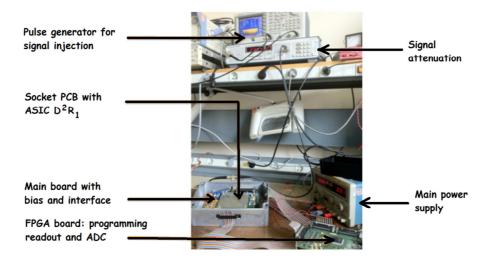

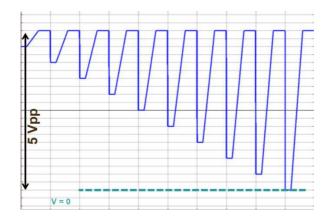

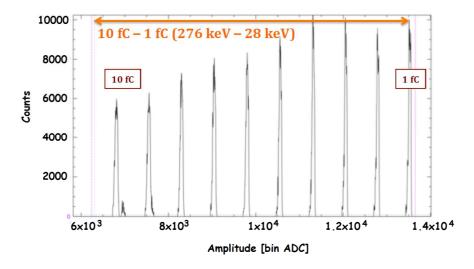

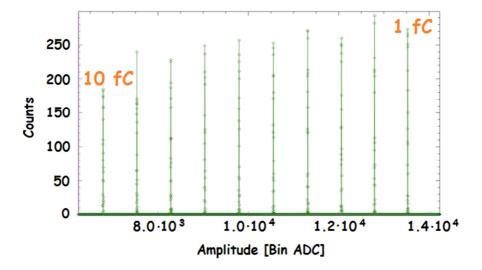

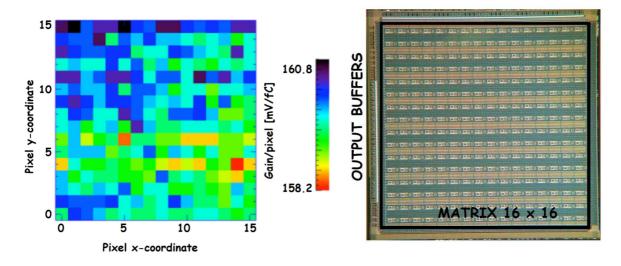

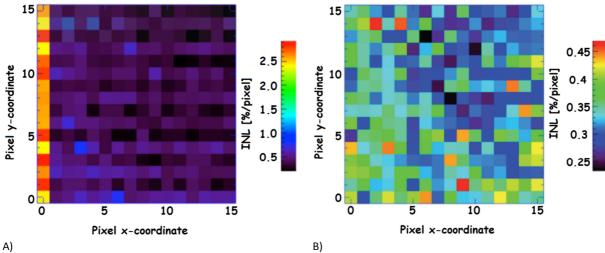

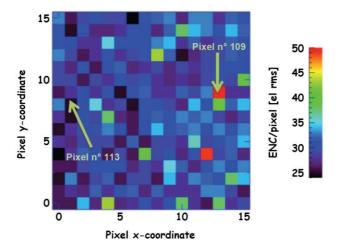

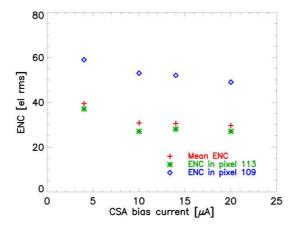

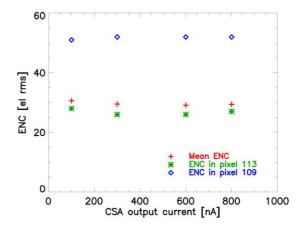

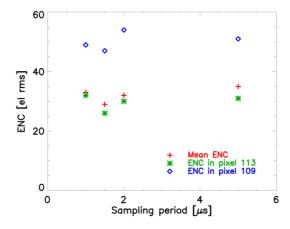

# 1.2.2.2. Charge loss: detector thickness vs. bias voltage