# Architecture systèmes Numériques

Hervé Le Provost

DSM/IRFU - CEA Saclay herve.le-provost@cea.fr

avec la participation de Shebli Anvar shebli.anvar@cea.fr

Version 2.0 – 2 octobre 2017

### Circuits numériques : la mémoire

## Circuits numériques : la mémoire

### Circuits numériques : la mémoire

- Mémoires non Volatiles

- ROM (Read Only Memory), programmée à la fabrication

- PROM (Programmable ROM), programmée une seule fois par l'utilisateur.

- ☐ EPROM (Erasable PROM), programmable plusieurs fois par l'utilisateur sur des machines dédiées

- ☐ EEPROM (Electrically Erasable PROM), programmable plusieurs fois par l'utilisateur in-situ

- Les plus utilisées : FLASH, BIOS carte mère PC. Rapides et haute densité (plusieurs Méga octets)

- NVRAM (Non volatile Random Access Memory)

- ☐ Mémoires Volatiles

- RAM (Random Access Memory), SRAM, SDRAM, DDR2, DDR3.

# Circuits numériques : codage des valeurs

| décimal | binaire | Hexa-<br>décimal |

|---------|---------|------------------|

| 0       | 0000    | 0                |

| 1       | 0001    | 1                |

| 2       | 0010    | 2                |

| 3       | 0011    | 3                |

| 4       | 0100    | 4                |

| 5       | 0101    | 5                |

| 6       | 0110    | 6                |

| 7       | 0111    | 7                |

| décimal | binaire | Hexa-<br>décimal |

|---------|---------|------------------|

| 8       | 1000    | 8                |

| 9       | 1001    | 9                |

| 10      | 1010    | A                |

| 11      | 1011    | В                |

| 12      | 1100    | С                |

| 13      | 1101    | D                |

| 14      | 1110    | Е                |

| 15      | 1111    | F                |

Valeur décimale 47, codage binaire et hexadécimal?

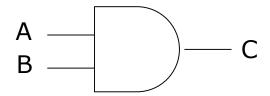

# Circuits numériques : portes logiques

EΤ

| Α | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Α |  | _  |

|---|--|----|

| В |  | —C |

OU

| Α | В | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| A - |            | <b>.</b>     |

|-----|------------|--------------|

| В-  | — <u> </u> | $\mathbf{E}$ |

OU EXCLUSIF

| Α | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

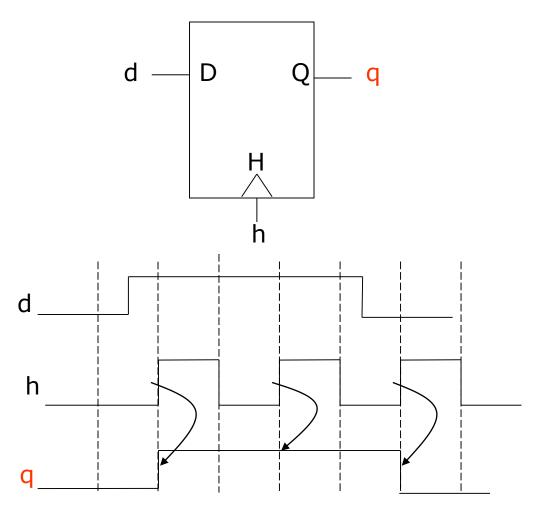

# Circuits numériques : Bascule D

Bascule D

| h        | D | $Q_{n+1}$      |

|----------|---|----------------|

|          | 0 | 0              |

| <u>_</u> | 1 | 1              |

| Ţ        | X | Q <sub>n</sub> |

| 0        | X | Q <sub>n</sub> |

| 1        | X | Q <sub>n</sub> |

Table de vérité

Chronogramme

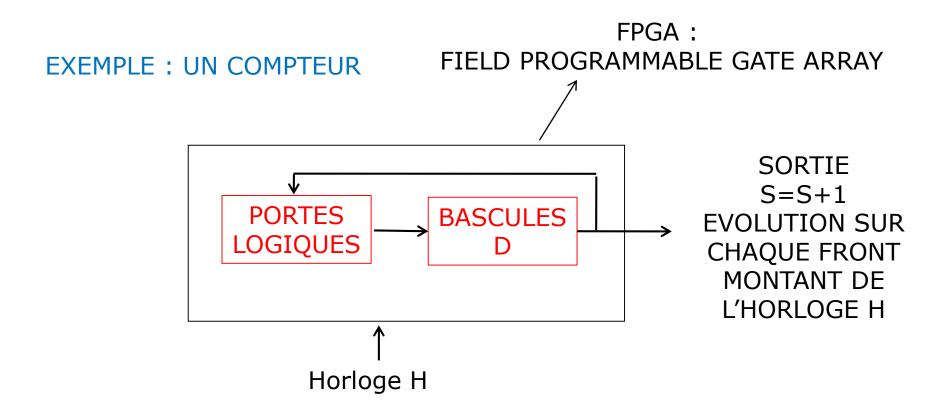

### Circuits numériques : Design Synchrone

FREQUENCE F=50 MHz, COMPTEUR S CODE SUR 8 BIT => QUELLE EST LA DUREE ECOULEE ENTRE 2 PASSAGE A 0 DU COMPTEUR ?

### Circuits numériques : un design, un LEGO

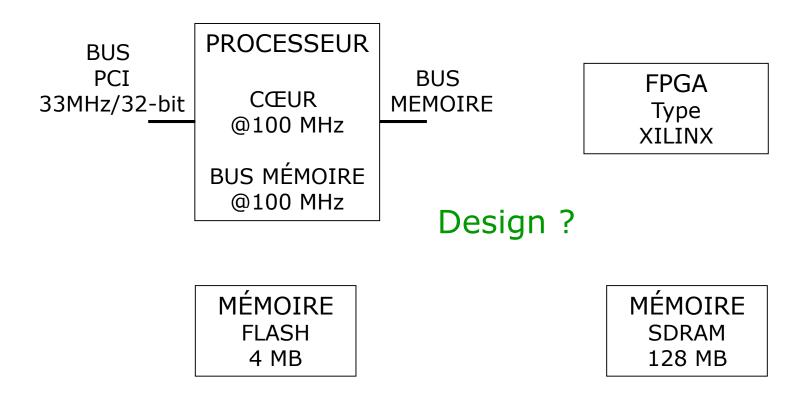

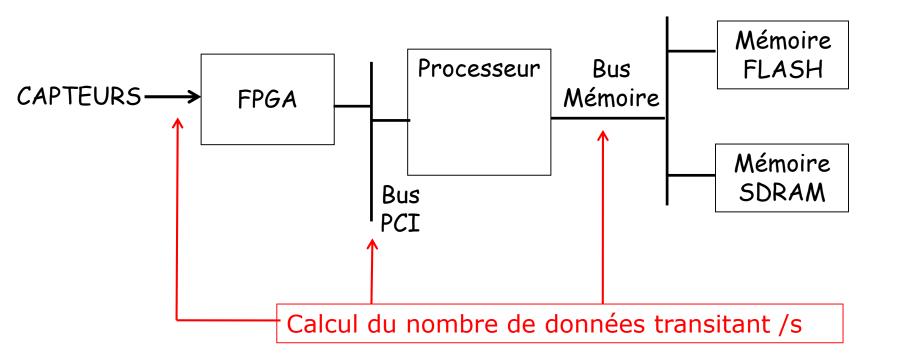

#### DESIGN: LECTURE DE CAPTEURS (FORMAT PROPRIETAIRE) ET TRAITEMENT DES DONNEES PAR UN PROCESSEUR TOURNANT UN SYSTÈME D'EXPLOITATION

# Circuits numériques : un design, un LEGO

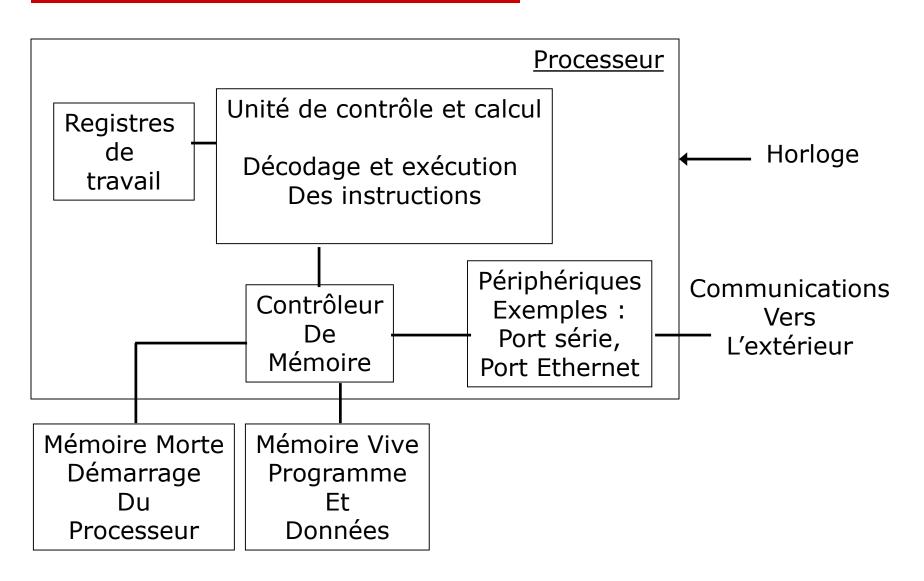

## Architecture générique d'une carte processeur

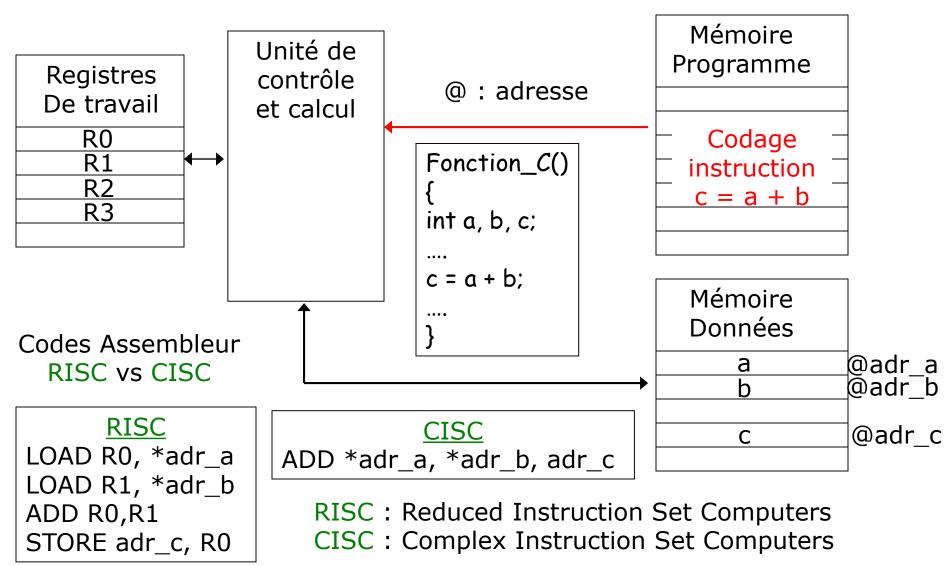

### Processeur et codage assembleur

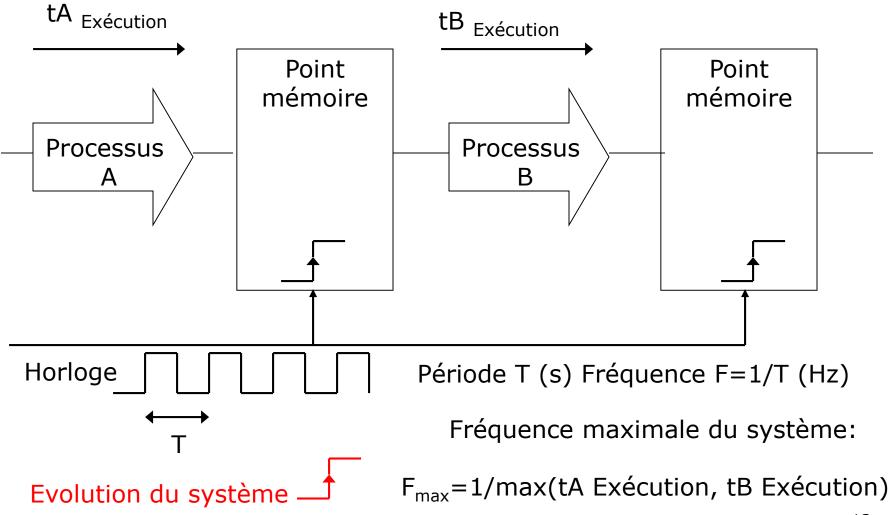

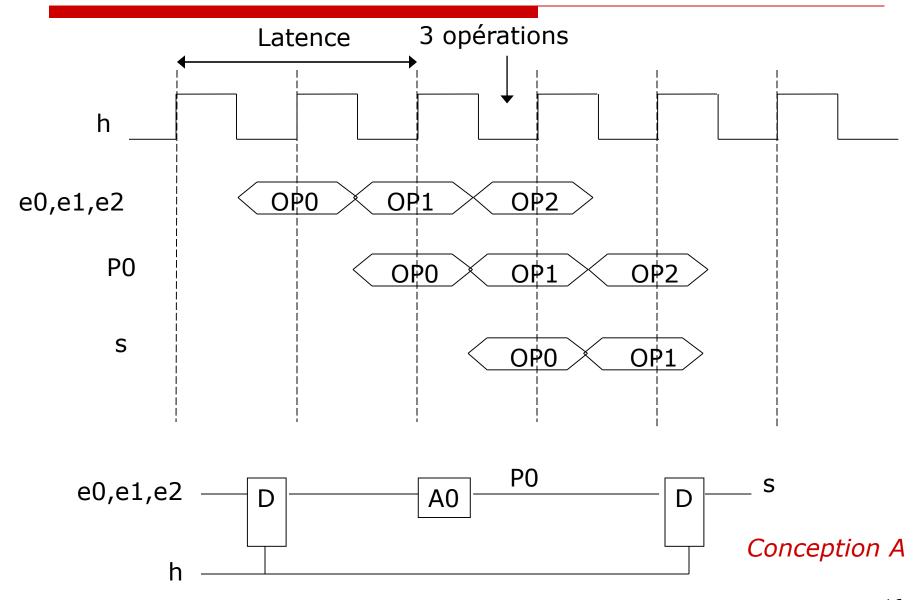

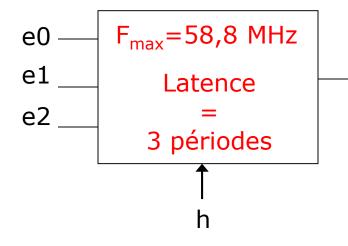

Proposer une solution pour augmenter la fréquence maximale de fonctionnement

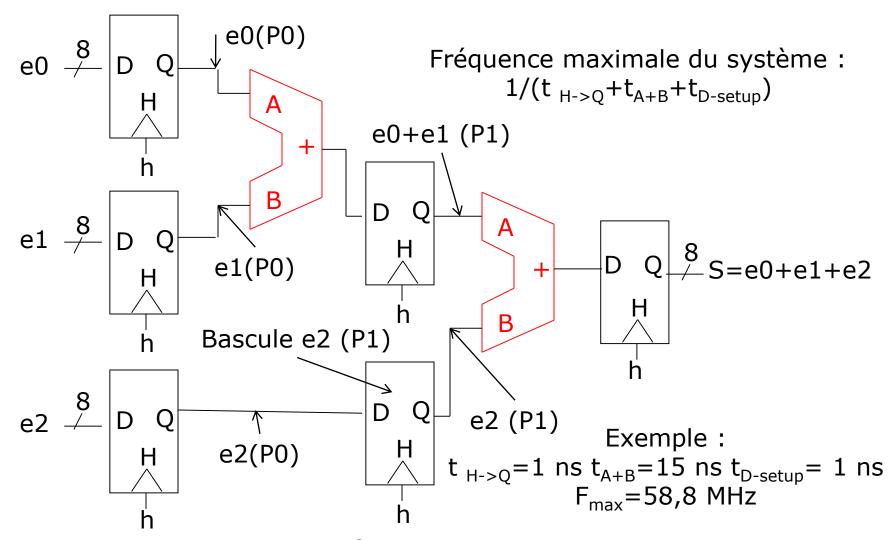

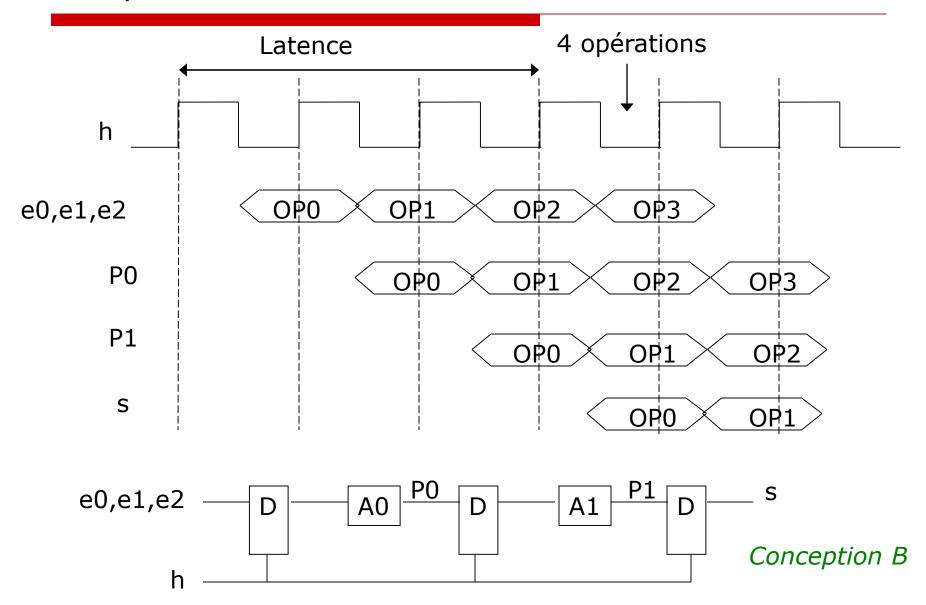

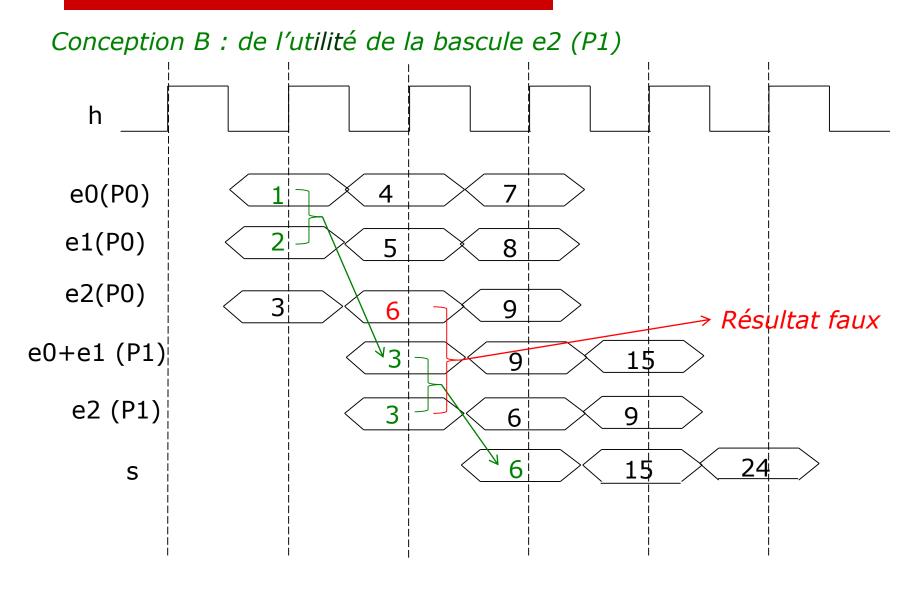

Conception B: ajout d'un étage de pipeline

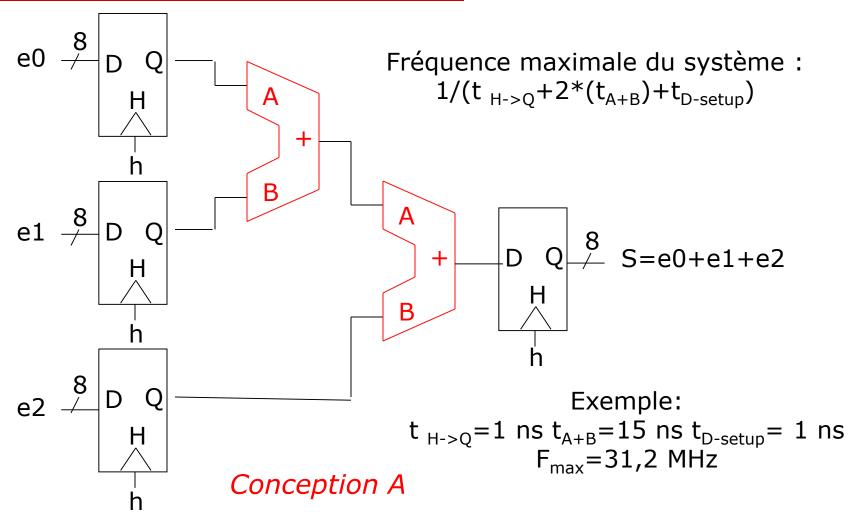

#### Conception A

S=e0+e1+e2

- 1. Des opérandes toutes les 32 ns. Un résultat toutes les 32 ns

- 2. Le temps de calcul d'une opération est de 2x32ns=64ns

#### Conception B

$$S=e0+e1+e2$$

- 1. Des opérandes toutes les 17 ns. Un résultat toutes les 17 ns

- 2. Le temps de calcul d'une opération est de 3x17ns=51ns

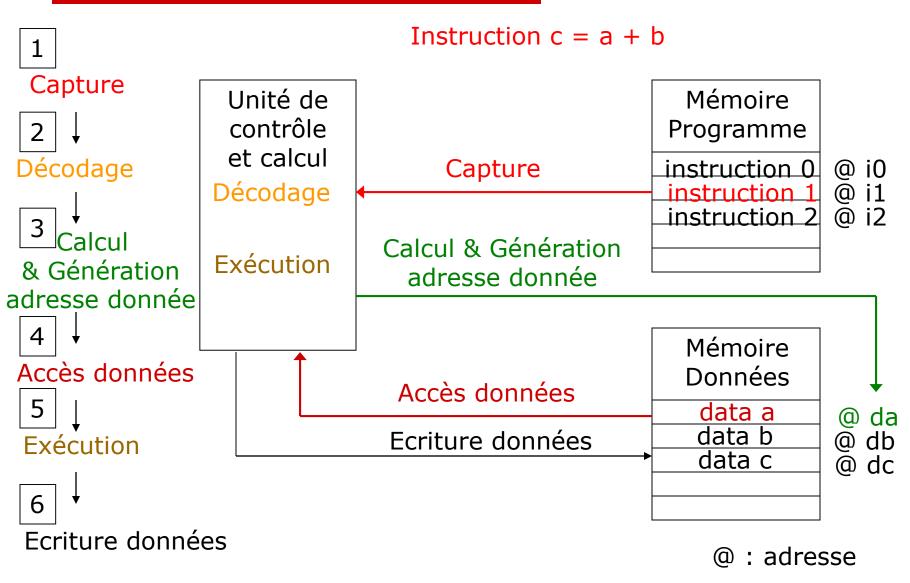

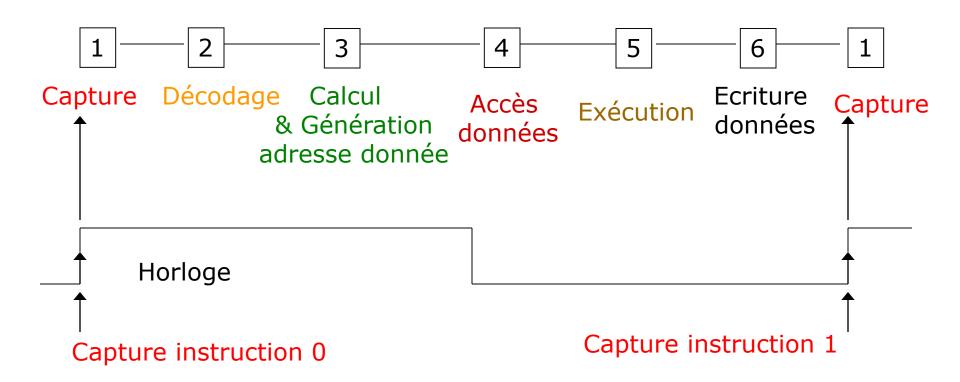

### Exécution d'une instruction

## Exécution séquentielle des instructions

Comment augmenter la fréquence maximale de capture des instructions ?

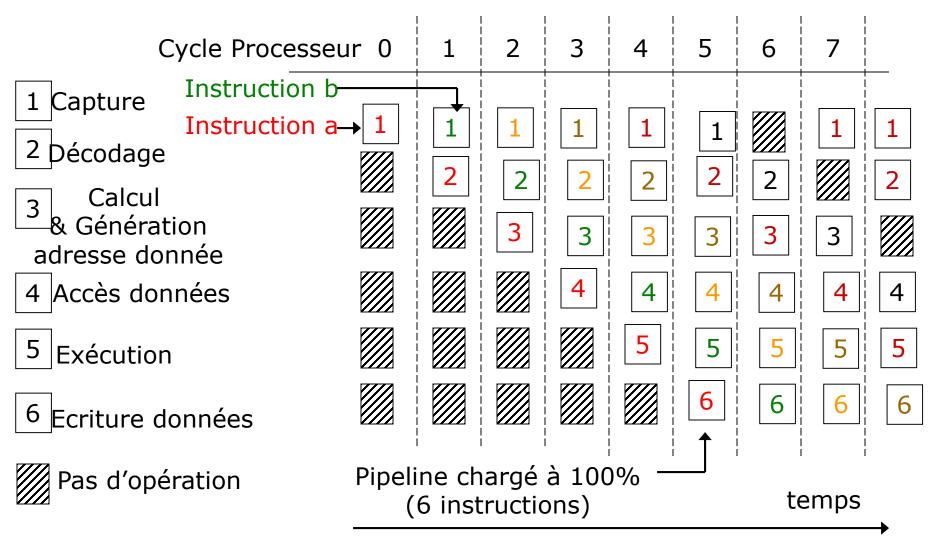

## Exécution en pipeline des instructions - Principe

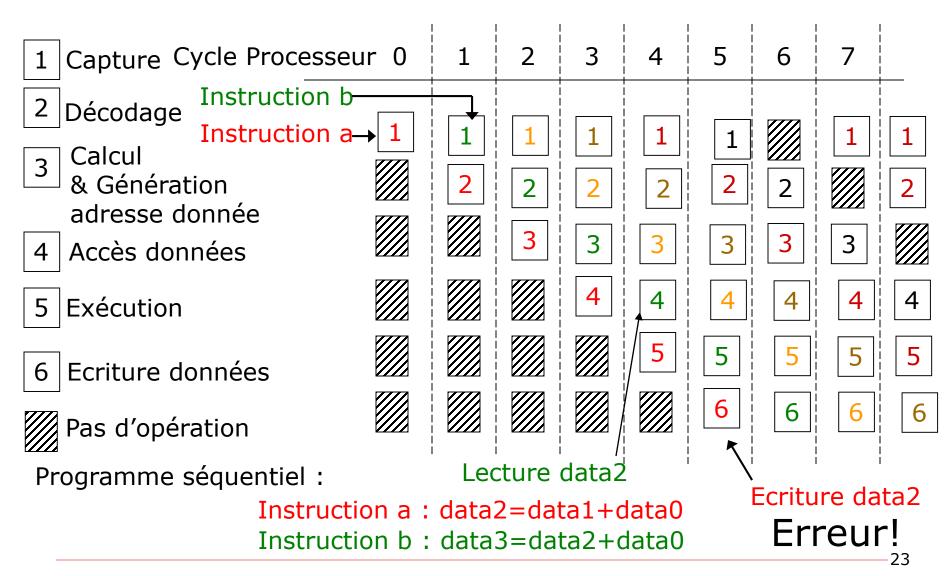

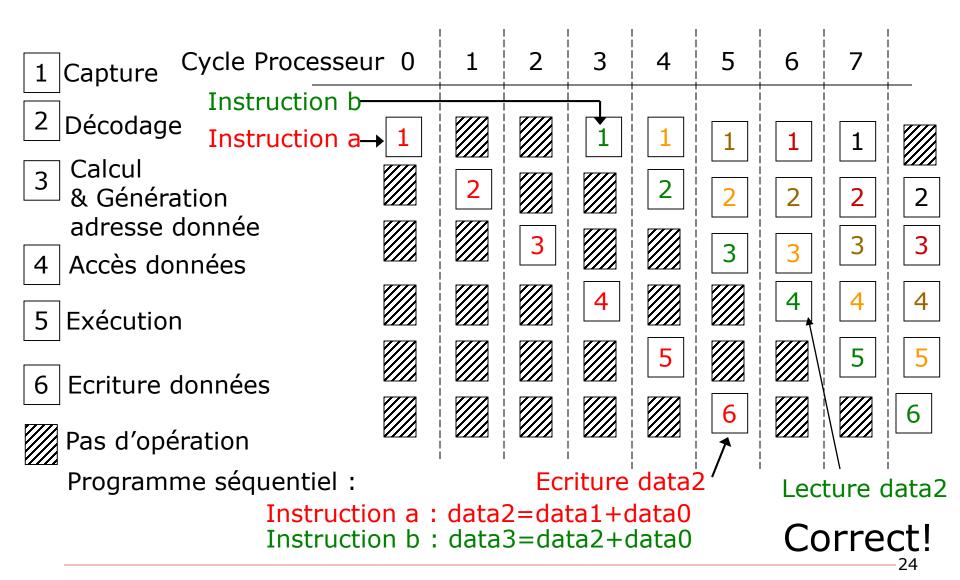

## Exécution en pipeline des instructions

## Exécution en pipeline des instructions

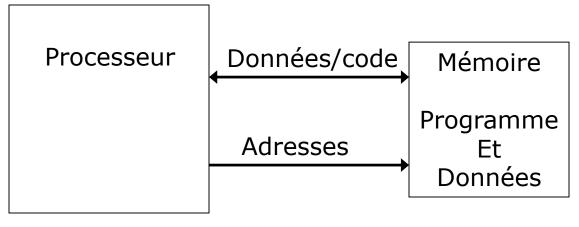

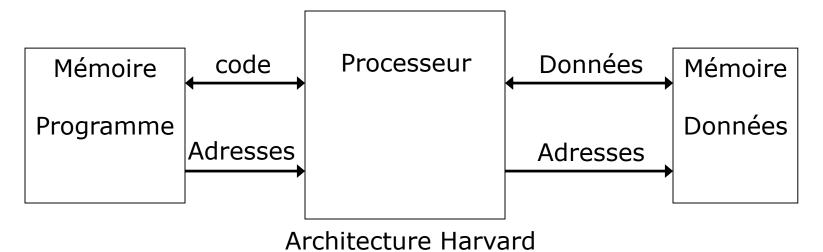

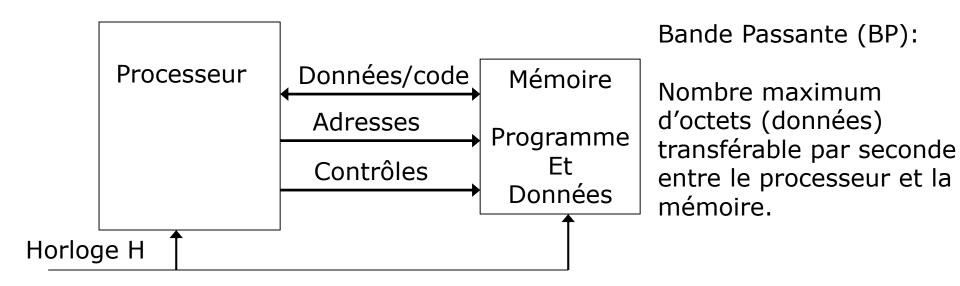

### Processeur et Mémoires

Architecture von Neumann

Quelle architecture est directement compatible avec une exécution en pipeline des instructions?

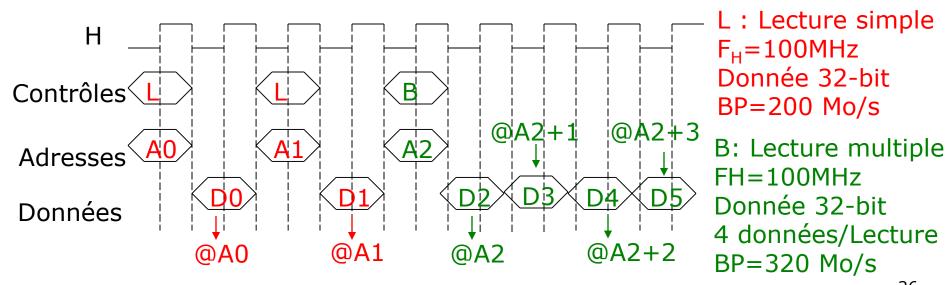

## Bande passante mémoire

### Calcul d'une bande passante

- Bus PCI (PC)

- Version 1.0 32-bit/33 MHz

- □ Bande passante?

- Version 2.1 64-bit/66 MHz

- □ Bande passante?

- PCI-X 2.0 64-bit/533MHz

- □ Bande passante?

- Bande passante vs Débit effectif

- Multiplexage Adresse/Données (PCI)

- Écriture vs lecture

- Accès simple vs bouffée

- Arbitrage sur le bus

- Partage code/données (von Neumann)

- Bande passante effective : données utiles transférées

# Évolution des Bus d'acquisition de données

```

ISA, Industry Standard Architecture (PC)

* PCI-E 1.1 (2 x 8 GO/s)

PCI, Peripheral Component Interconnect (PC)

* PCI-X 2.0 (4,3 GO/s)

AGP, Accelerated Graphic Port (PC)

* AGP 8x (2,1 GO/s)

VME, Versa Module Eurocard

* PCI-X 1.0 (1 GO/s)

Débit

* PCI 2.1 (528 MO/s)

Max.

* VME2ESST (320 MO/s)

* PCI 1.0 (132 MO/s)

* VME64 (80 MO/s)

* VME32 (40 MO/s)

* ISA (16,7 MO/s)

* ISA (4,8 MO/s)

1981 1982 1984 1992 1994 1995 1998 1999

2002 2003

Année

```

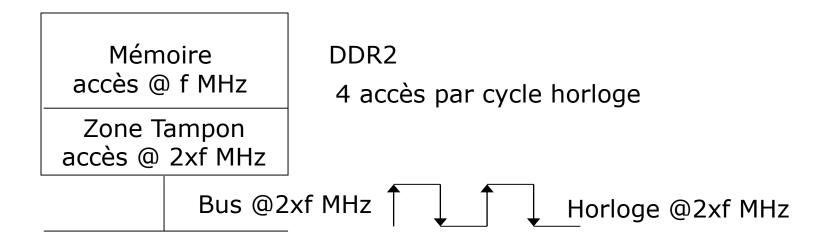

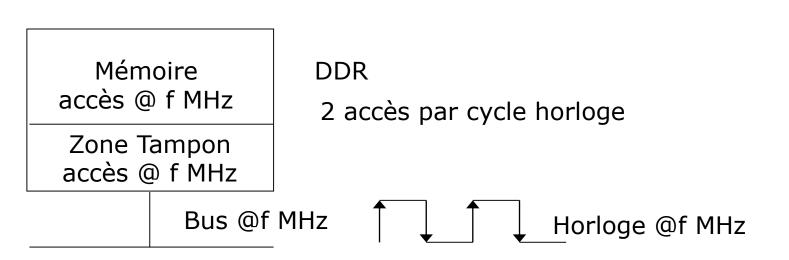

### Mémoire SDRAM DDR2 versus SDRAM DDR

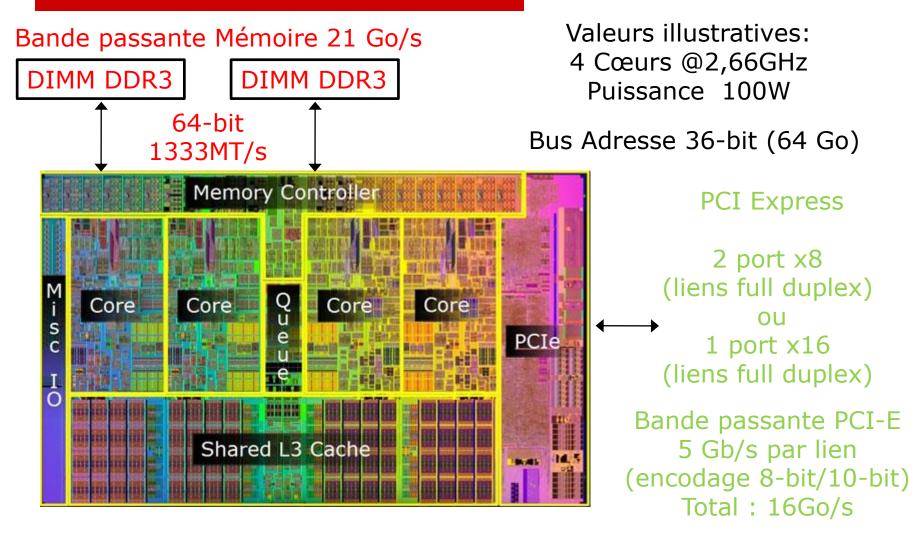

### Exemple: le processeur Intel Core I5-700

Sources: dessin <u>www.hardware.fr</u> Données techniques: Intel Core i7-800 and i5-700 Desktop processors series, datasheet-Volume 1, September 2009, Intel

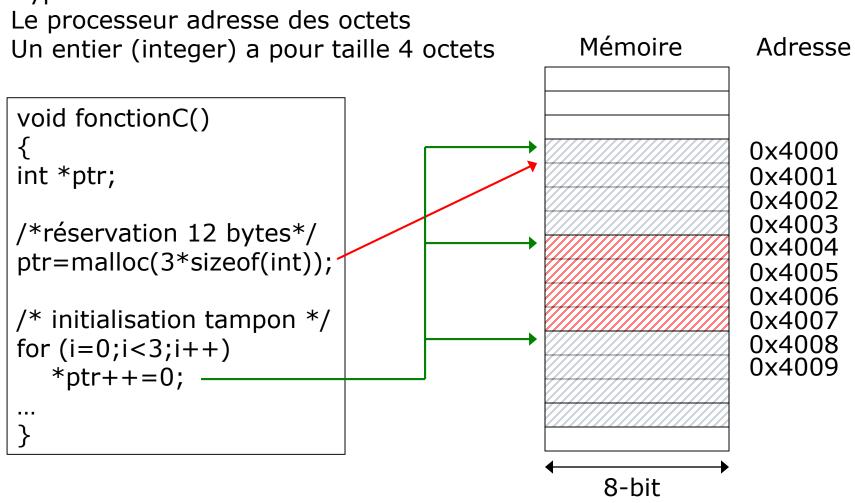

## Organisation mémoire

### Hypothèses:

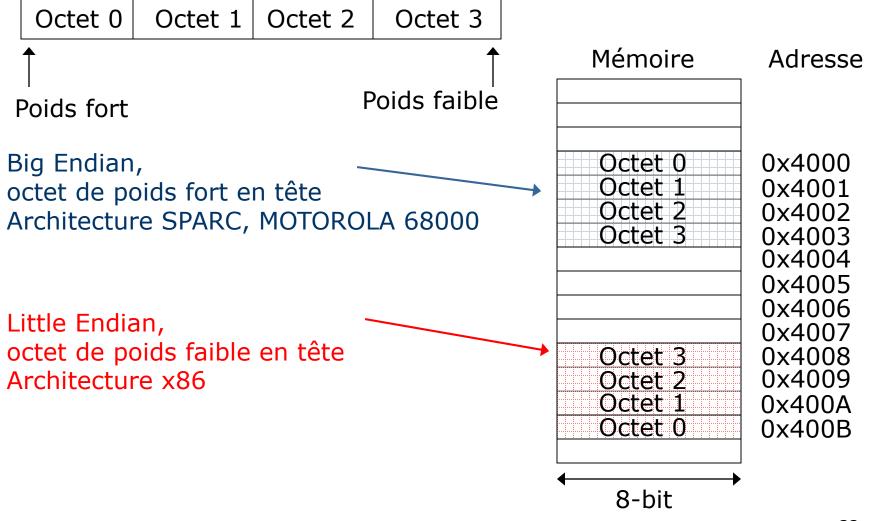

## Organisation mémoire: Big Endian vs Little Endian

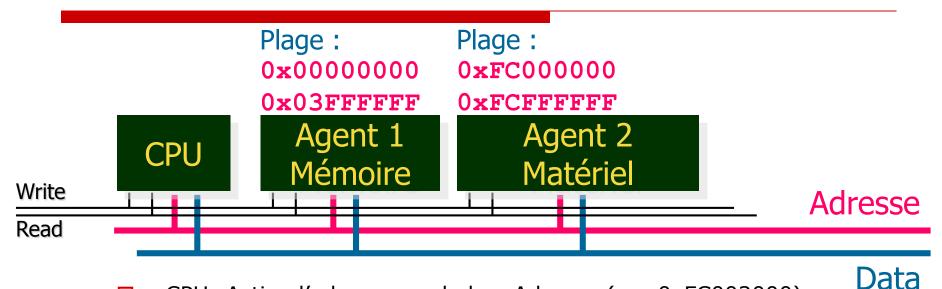

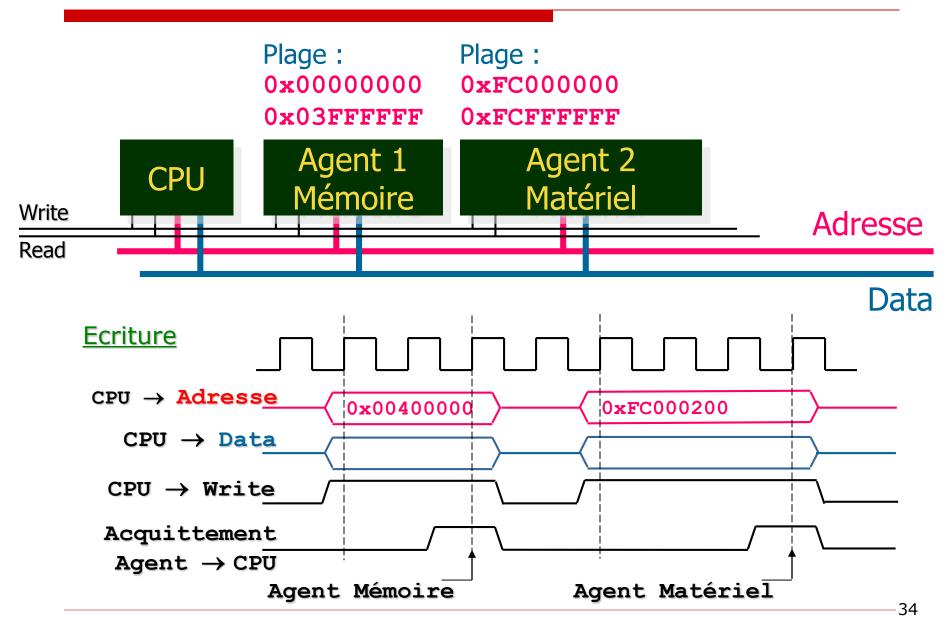

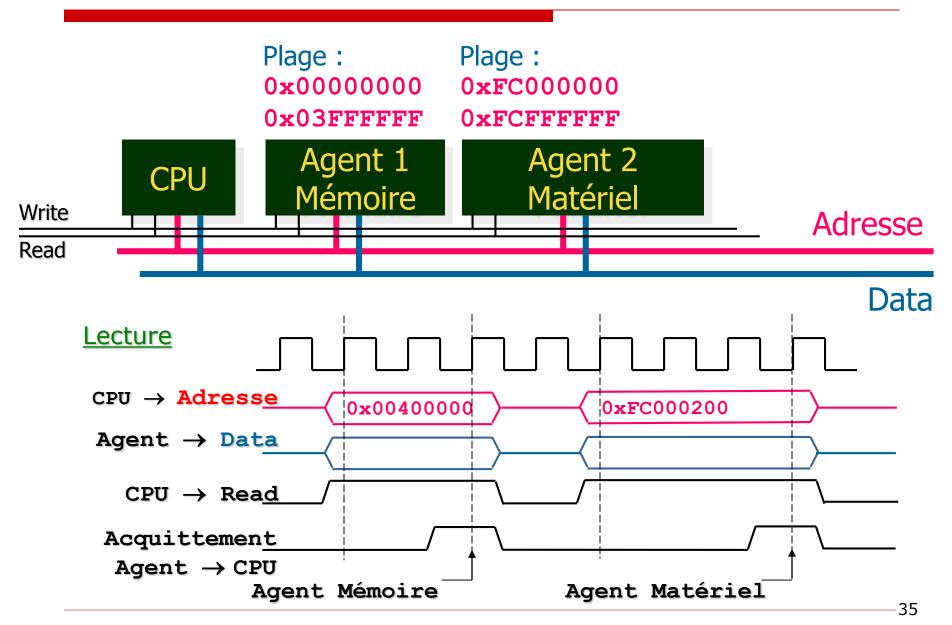

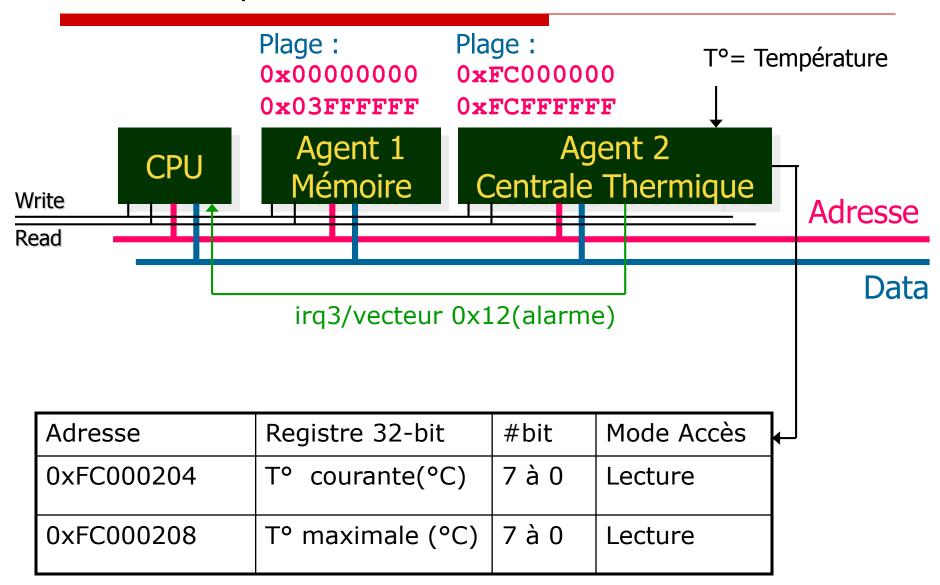

- $\square$  CPU: Active l'adresse sur le bus Adresse (ex: 0xFC002000).

- ☐ Périphérique : un seul est sensible à cette adresse

- □ Si écriture :

- CPU active la donnée sur le bus Data.

- Périphérique : concerné traite la donnée sur le bus Data.

- ☐ Si lecture:

- Périphérique : active la donnée sur le bus Data.

- CPU : traite (lis) la donnée sur le bus Data.

- Modes de lecture/écriture spéciaux (rafale synchrone, etc.)

- Contrôleur mémoire : séparé ou intégré au CPU

© Shebli Anvar

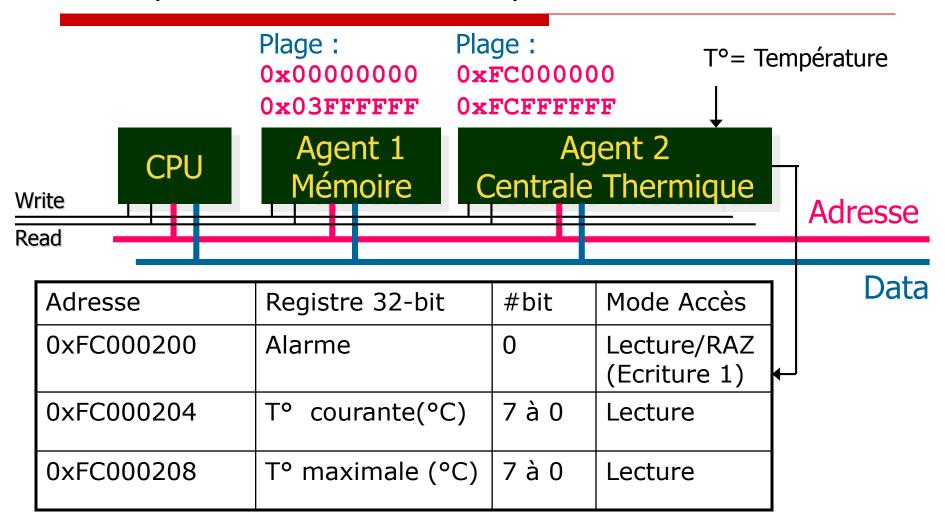

Ecrire le code C qui sur alarme affiche la température courante et maximale et efface l'alarme

### Principe de communication par bus

```

void alarm() {

volatile unsigned int *ptr1, *ptr2, *ptr3;

int alarme, TO, T1;

ptr1=(unsigned int*)0xFC000200;//alarme

ptr2=(unsigned int*)0xFC000204;//T° courante

ptr3=(unsigned int*)0xFC000208;//T° maximale

while (1) {

alarme=*ptr1&1;

if (alarme!=0) {

TO=(*ptr2)&255;//lecture T° courante

T1=(*ptr3)&255;//lecture T° maximale

printf («Temp. courante %d maximale %d\n», TO, T1);

*ptr1=1;//RAZ alarme

```

Quel est l'impact de ce code sur les performances du CPU?

#### Exercice 1

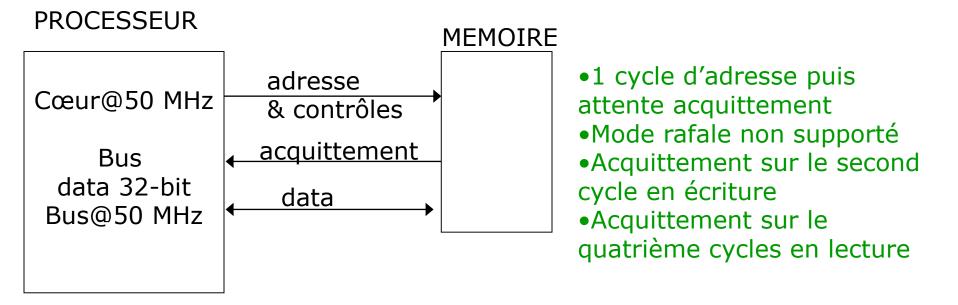

Calcul de la bande passante (Mo/s) effective en écriture

Calcul de la bande passante (Mo/s) effective en lecture

#### Correction Exercice 1

#### Calcul de la bande passante effective en écriture

3 cycles@50MHz (60ns) pour transférer 4 octets 4/(60ns) = 66,7 Méga octets transférées en 1s

$BP_{\text{\'e}criture} = 66,7 \text{ Mo/s}$

#### Calcul de la bande passante effective en lecture

5 cycles@50MHz (100ns) pour transférer 4 octets 4/(100ns) = 40 Méga octets transférées en 1s

$$BP_{Lecture} = 40 \text{ Mo/s}$$

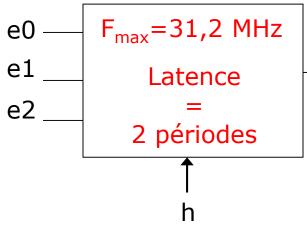

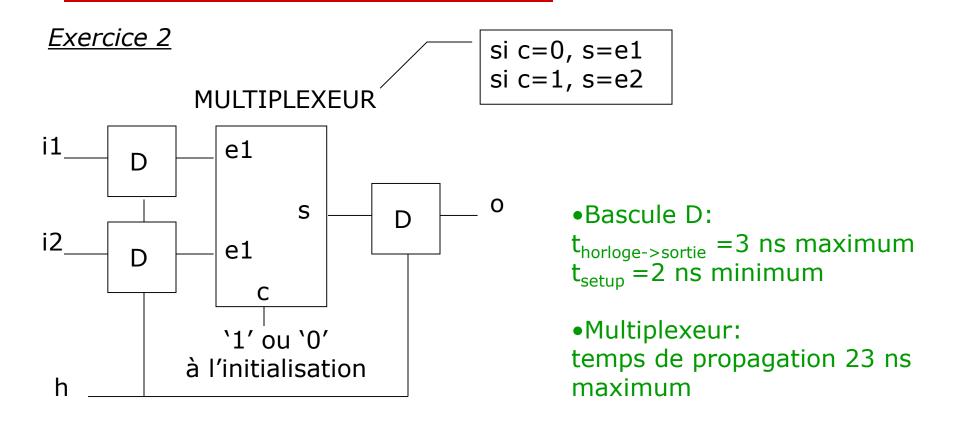

Calcul de la fréquence maximale de fonctionnement

#### **Correction Exercice 2**

#### Calcul de la fréquence maximale de fonctionnement

$$F_{max} = 1/(t_{horloge->sortie} + t_{setup} + t_{prop. Mux.})$$

$$F_{max} = 1/(3 \text{ ns} + 2 \text{ ns} + 23 \text{ ns})$$

$$F_{max} = 35,7 \text{ MHz}$$

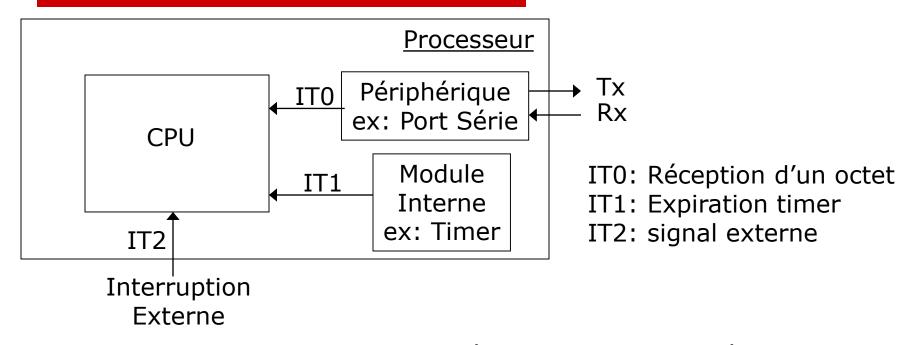

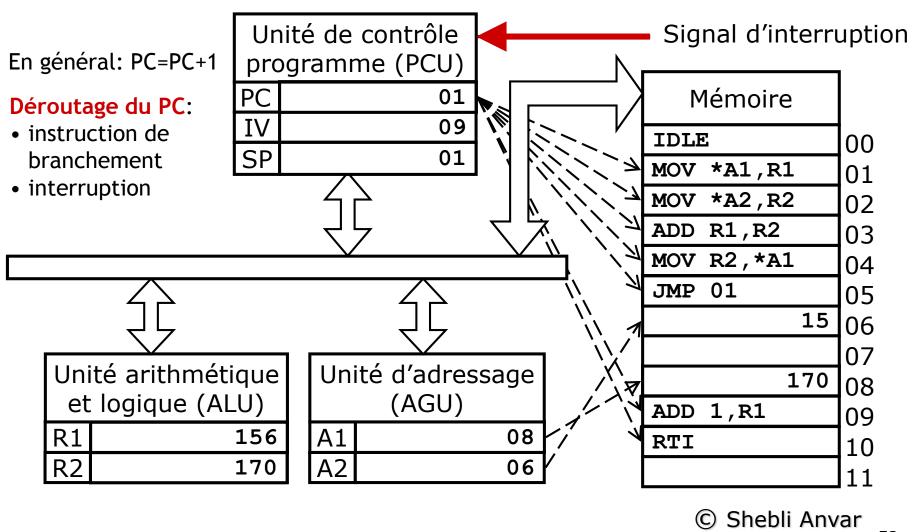

- L'autre moyen de communication entre un périphérique et le CPU est l'interruption matérielle. C'est la seule communication qui soit *initiée à l'initiative du périphérique (esclave)*.

- Son fonctionnement exact dépend de l'architecture matérielle de la carte et des liaisons entre le périphérique et les broches d'interruption du CPU.

- ☐ Le CPU associe à une broche une fonction d'interruption. Dans cette fonction, l'interruption est traitée. Si le CPU est animé par un OS :

- Tous les appels susceptibles d'être bloquants sont interdits au sein de la fonction d'interruption.

- Le temps d'exécution de l'interruption doit être minimisé. Tout traitement lourd doit être effectué par une tâche standard en attente de libération d'un sémaphore. Ce sémaphore est libéré par la fonction d'interruption

Interruption (IT) ISR: Interrupt Service Routine matérielle/logicielle nº i PC: Program Counter void routineEnCours() Sauvegarde registres d'état, PC (@inst(d=a-b)) sur la pile c=a+b; //PC=@inst(c=a+b) d=a-b; //PC=@inst(d=a-b) Recherche adresse vecteur interruption dans table à partir 6 du nom du vecteur ou du nº IT, chargement du PC avec adresse Restitution registres d'état, n<sup>0</sup> IT Adresse Vecteur IT PC (@inst(d=a-b)) de la pileadresse ISR(0) 0 5 adresse ISR(1) Exécution routine d'interruption ISR(i) adresse ISR(2) void ISR() {....} 4

- ☐ Interruption externe asynchrone, sélection front montant, état

- Trois principaux registres d'interruption:

- Registre d'autorisation individuelle

- Registre de présence individuelle

- Registre de remise à zéro individuelle

- Priorités entre les interruptions définies par le processeur cible

- ☐ Sur interruption, sauvegarde automatique du PC et des registres d'état sur la pile

```

//Exemple gestion interruptions-Système exploitation RTEMS

void initSystem() {

rtems_status_code status;

rtems_isr_entry old_handle;

//...

status=rtems_interrupt_catch(alarmCatch, 0x12,&old_handle);

//...

rtems_isr alarmCatch(rtems_vector_number vector) {

volatile unsigned int *ptr2, ptr3;

int TO, T1;

ptr2=(unsigned int*)0xFC000204;//T° courante

ptr3=(unsigned int*)0xFC000208;//T° maximale

TO=(*ptr2)&255;//lecture T° courante

T1=(*ptr3)&255;//lecture T° maximale

printk («Temp. courante %d maximale %d\n», T0, T1);

```

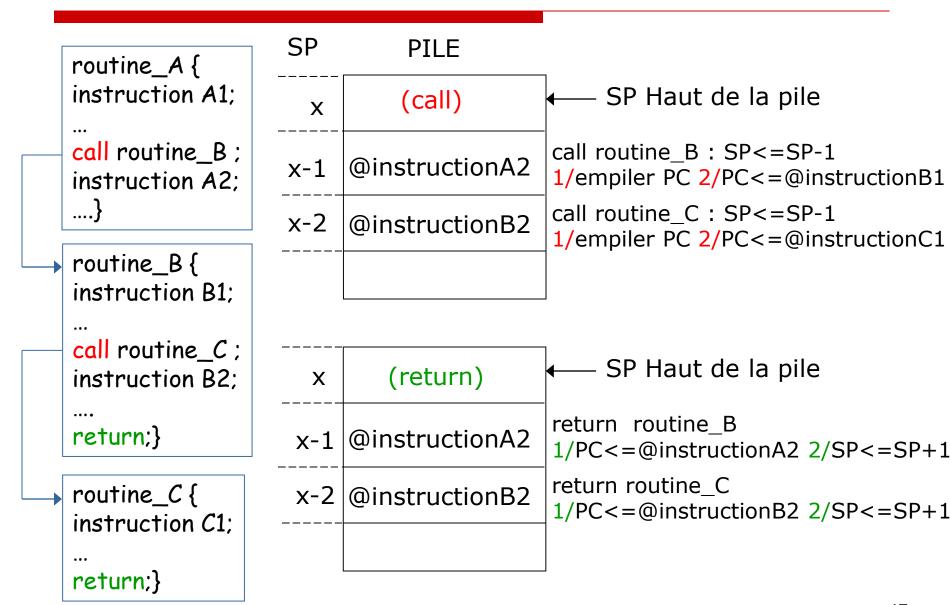

### La Pile: Principe

### La Pile: variables automatiques

| SP  | PILE |  |

|-----|------|--|

| X   |      |  |

| x-1 | С    |  |

| x-2 | b    |  |

| x-3 | a    |  |

|     |      |  |

- 1 Décrémentation SP de 3/Réservation mémoire pour `a','b','c'

- 2 Stockage valeurs 'a','b' sur la pile

- 3 Accès aux variables depuis la pile pour exécution du calcul

- 4 Stockage résultat 'c' sur la pile

- 5 Incrémentation SP de 3/Libération mémoire

### La Pile : variables automatiques

```

; codage assembleur DSP TMS320C55

;int main()

Adresse instruction

Décrémentation

; {

Code machine

pointeur de pile

01418F

main:

AADD #-3,SP

01418F 4efd

;int a=3,b=5,c;

MOV #3,*SP(#00h)

014191 e60003

Stockage valeurs

MOV #5,*SP(#01h)

014194 e60205

a et b sur la pile

; c=a+b;

014197 a902

MOV *SP(#01h),AR1

Calcul

014199 d60099

ADD *SP(#00h),AR1,AR1

01419C c904

MOV AR1, *SP(#02h)

Stockage résultat

;return 0;

MOV #0,T0

01419E 3c04

Sur la pile

; }

0141A0 4e03

AADD #3,SP

0141A2 4804

RET

```

# La Pile : passage des paramètres

```

int main()

int a=1,b=2,c=3,d=4,e=5,f=6,g=7,h=8;

int r:

r=addition(a,b,c,d,e,f,g,h);

return 0:

int addition(int a,int b,int c,int d,int e,

int f,int g,int h)

int r;

r=a+b+c+d+e+f+g+h;

return r:

```

| SP         | PILE          | SP à l'entrée<br>du main() | 9               |

|------------|---------------|----------------------------|-----------------|

| X          |               |                            |                 |

| x-1        | r             | SP(10)                     |                 |

| x-2        | h=8           | SP(9)                      |                 |

| x-3        | g=7           | SP(8)                      | <               |

| x-4        | f=6           | SP(7)                      | aria            |

| x-5        | e=5           | SP(6)                      | ble             |

| x-6        | d=4           | SP(5)                      | variables auto. |

| x-7        | c=3           | SP(4)                      | οιη             |

| x-8        | b=2           | <u>SP(3)</u>               | •               |

| x-9        | a=1           | SP(2)                      |                 |

| x-10       |               | SP(1)                      |                 |

| x-11       | h (paramètre) | SP(0)                      |                 |

| <b>-</b> - |               |                            |                 |

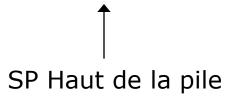

- ☐ Paramètres a, b, c, d, e, f, g passés par registre, paramètre h passé sur la pile

- Retour r passé par registre

- Dépendant du couple compilateur/cible, du niveau d'optimisation du compilateur

SP avant appel addition()

-50

# La Pile : passage des paramètres

| 01418F 4ef5   | AADD #-11,SP ────── | Décrémentation           |

|---------------|---------------------|--------------------------|

| 014191 e60401 | MOV #1,*SP(#02h)    | oointeur de pile         |

| 014194 e60602 | MOV #2,*SP(#03h)    |                          |

| 014197 e60803 | MOV #3,*SP(#04h)    |                          |

| 01419A e60a04 | MOV #4,*SP(#05h)    | Stockage valeurs de      |

| 01419D e60c05 |                     | 3 variables sur la pile  |

| 0141A0 e60e06 | MOV #6,*SP(#07h)    | μ                        |

| 0141A3 e61007 | MOV #7,*SP(#08h)    |                          |

| 0141A6 e61208 | MOV #8,*SP(#09h)    |                          |

| 0141A9 a912   | MOV *SP(#09h),AR1 P | assage de 1 paramètre    |

| 0141AB c900   | MOV AR1,*SP(#00h) p | ar la pile               |

| 0141AD a404   | MOV *SP(#02h),T0    | -<br>-                   |

| 0141AF a506   | MOV *SP(#03h),T1    |                          |

| 0141B1 a808   | MOV *SP(#04h),AR0   | assage de 7 paramètres   |

| 0141B3 aa0c   | MOV "SP(#UOII), ARZ | -                        |

| 0141B5 ab0e   | MOV *SP(#07h),AR3   | ar registre              |

| 0141B7 ac10   | MOV *SP(#08h),AR4   |                          |

| 0141B9 a90a   | MOV *SP(#05h),AR1   |                          |

| 0141BB 080008 | CALL addition       | Appel addition           |

| 0141BE c414   | MOV T0, *SP(#0ah)   |                          |

| 0141C0 3c04   | MOV #0, T0          | Stockage résultat sur la |

| 0141C2 4e0b   | AADD #11,SP         | oile                     |

| 0141C4 4804   | RET                 | 51                       |

# La Pile : passage des paramètres

### Fonctionnement du processeur

#### Animation PowerPoint

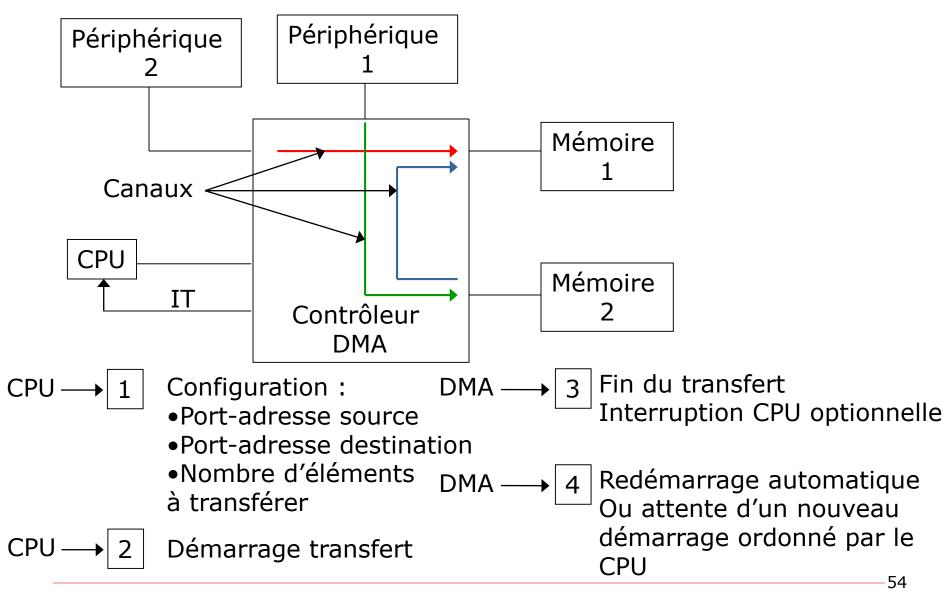

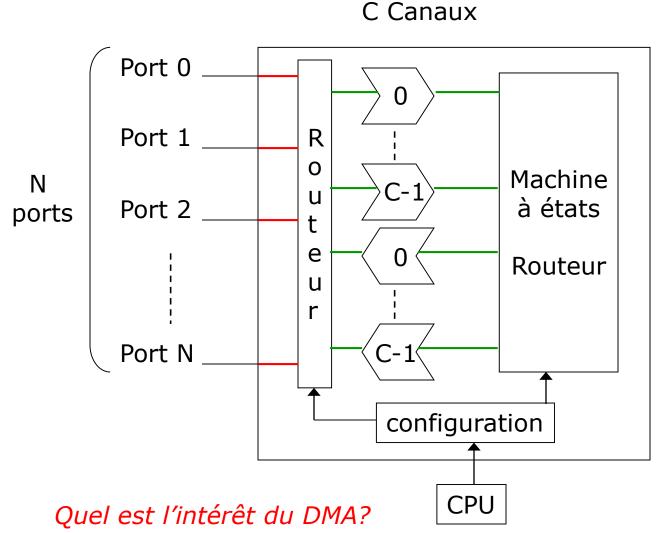

# DMA (Direct Memory Access): principe

### DMA: exemple

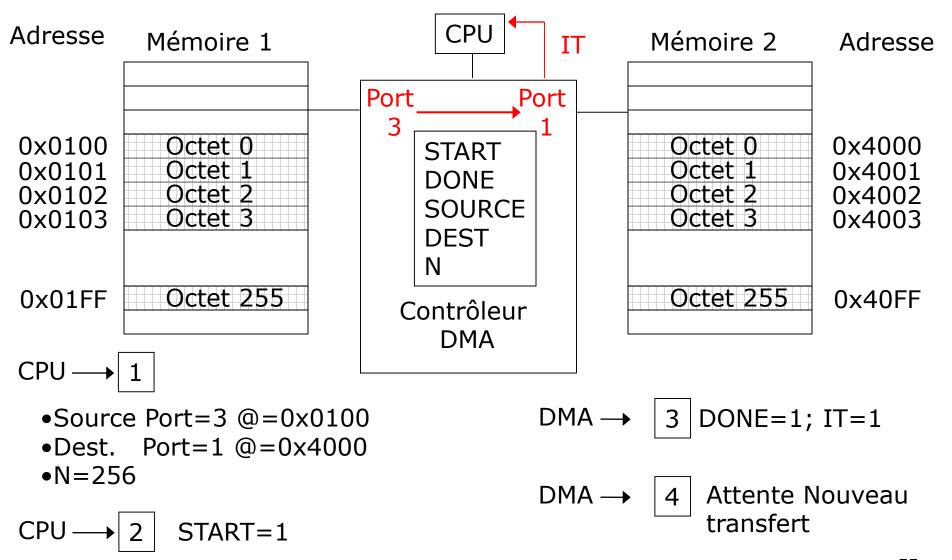

#### DMA: structure interne

- •Limitation du nombre de canaux

- •Distinction entre canaux et ports

- Port connectable sur lui-même

#### Développement d'un système informatique temps réel

- Maîtrise fine du système:

- Matériel

- □ La bande passante et la gestion de la mémoire

- La pile

- □ Le pipeline des données et des instructions

- □ La fréquence de fonctionnement

- Logiciel

- La chaine de compilation et ses niveaux d'optimisation et interactions avec le matériel.

- Le langage assembleur pour les portions critiques

- ☐ Les éléments de performance

- Les interruptions

- Le DMA

- La mémoire cache (seconde partie du cours)

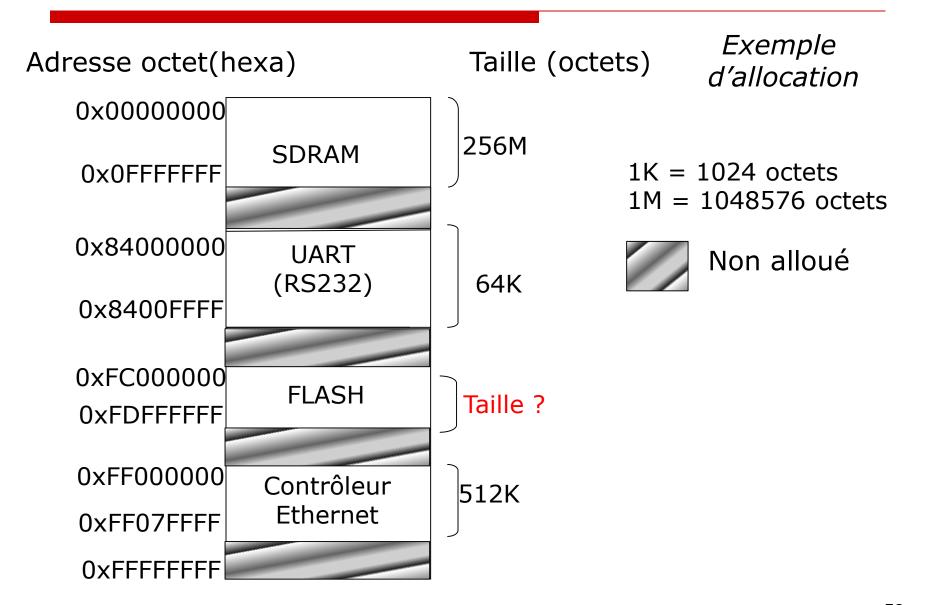

# La mémoire : les plages (vue du processeur)

# Systèmes multitâches

- Appel régulier d'un ordonnanceur

- •Régularité assurée par une alarme électronique (hardware timer)

- •TICK = période de cette alarme (typiquement ~10 ms)

- •Préemption: appel de l'ordonnanceur par interruption

- •L'alarme active un signal d'interruption

- •La routine associée à l'alarme d'ordonnancement est le code de l'ordonnanceur

- Le code de l'ordonnanceur « active » une tâche

- •Considère la liste des données liées à la gestion des tâches

- •Sauvegarde le contexte de la tâche en cours

- •Décide par un algorithme de la tâche à activer

- •Restaure le contexte de la tâche élue

- •Contexte  $\supseteq$  valeurs des registres du processeur, notamment le PC