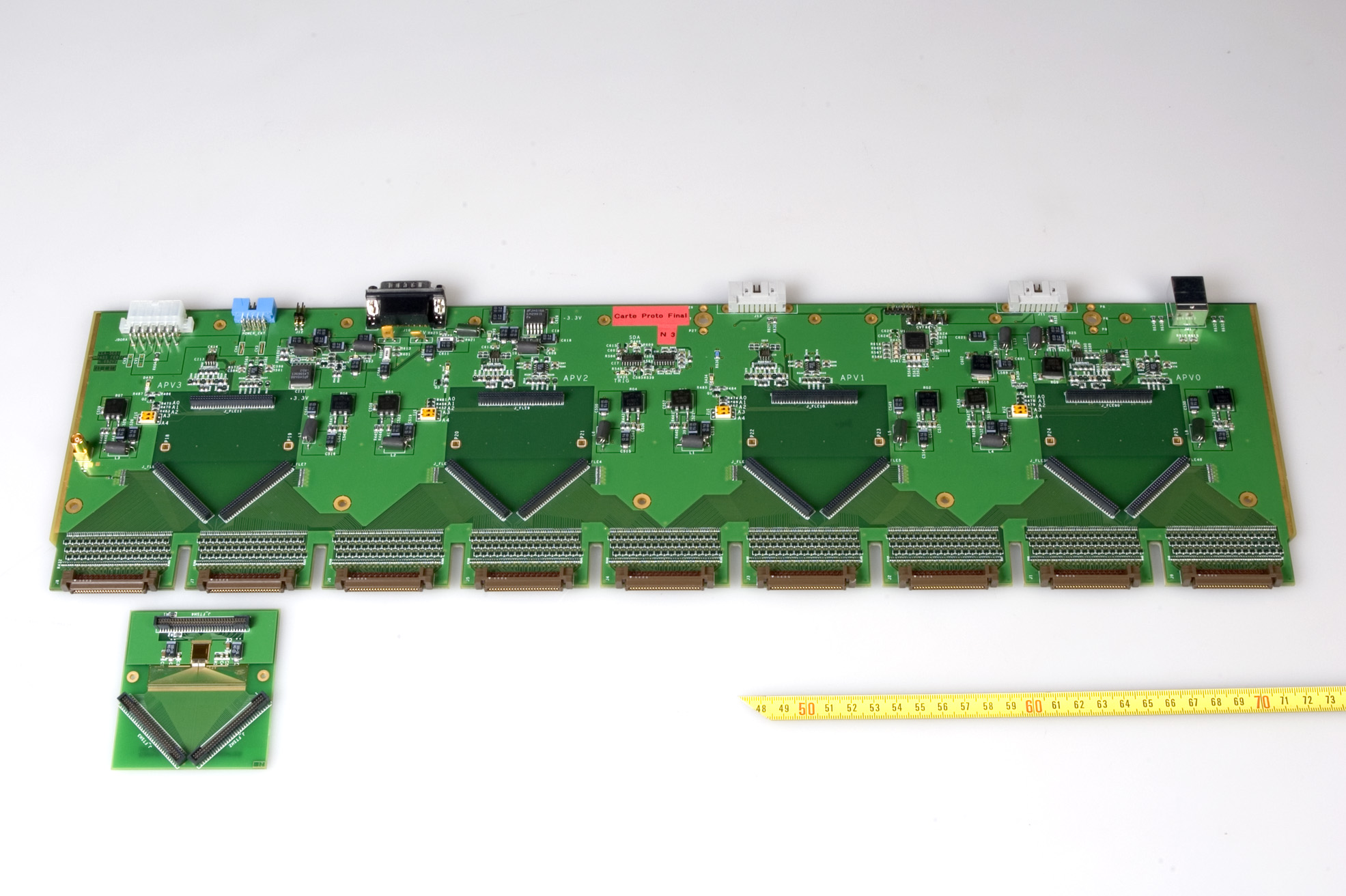

Carte frantale pour la lecture du détecteur Rich de Compass. Chaque carte-mère (en haut) accueille 4 carte-filles (en bas) intégrant une puce APV traitant 128 voies.

Si les chaînes de traitement de données sont devenues majoritairement numériques, les circuits frontaux, convertissant les signaux des détecteurs en grandeurs électriques, restent analogiques. Lorsque le nombre de voies est faible, les progrès réalisés sur les circuits commerciaux permettent un traitement toujours plus rapide et plus performant des informations. La segmentation de plus en plus fine des détecteurs conduit à un nombre croissant de voies électroniques qui impose l’utilisation d’une microélectronique de lecture. Outre la miniaturisation, l’utilisation de circuits intégrés spécifiquement conçus (asic, pour Application-Specific Integrated Circuit) permet une réduction de la puissance électrique consommée et du coût unitaire d’une voie électronique. Bien qu’ils comprennent essentiellement des fonctions analogiques, les asics modernes sont aujourd’hui des circuits mixtes analogiques et numériques pouvant intégrer, par exemple, des séquenceurs ou des fonctions de traitements de signaux. Leurs paramètres sont généralement configurables. Les asics conçus au Dapnia sont classés en trois grandes familles : les mémoires analogiques, les circuits à bas niveau de bruit, de basse consommation et les Maps (Monolithic Active Pixel Sensors).

Le Dapnia possède une expertise de plus de 10 ans dans le domaine des mémoires analogiques pour l’acquisition à haute fréquence de signaux de grande dynamique. La dernière mémoire conçue au Dapnia, SAM, produite à 6 000 exemplaires, permet la numérisation, à une fréquence d’un gigahertz et sur 12 bits de précision, des signaux de l’expérience Hess2.

Dans la seconde famille, on trouve les circuits Idef-X développée pour la spectrométrie gamma spatiale à base de détecteurs CdTe, dont le dernier prototype destiné au satellite SVOM/Eclairs. Au confluent des deux premières familles, l’asic After, développé pour l’expérience d’oscillation de neutrinos T2K, comporte 72 canaux de préamplification et de filtrage ainsi qu’une mémoire analogique. C’est le plus gros circuit (500 000 transistors) jamais conçu au Dapnia.

Les Maps, dans la troisième famille, associent sur un même substrat un détecteur et son électronique de proximité. Les puces Mimosa8 et 16, qui intègrent, pour la première fois, une électronique rapide réalisant des traitements évolués, ont démontré la faisabilité d’un trajectographe à base de Maps pour les collisionneurs du futur. Le Dapnia possède également un savoir-faire dans les tests et la mise en œuvre d’asics embarqués. Une nouvelle électronique à très bas bruit, basée sur les puces APV conçues au Rutherford Appleton Laboratory, a été réalisée, dans un temps très court, pour lire les 65 000 voies du détecteur Rich de l’expérience Compass

• Détection des rayonnements › Electronique et traitement du signal

• Le Département d'Électronique des Détecteurs et d'Informatique pour la Physique (DEDIP)

• Antares, un télescope à neutrinos de haute énergie • L'expérience COMPASS • SVOM • H.E.S.S. • MUST2 : MUr à STrips • T2K