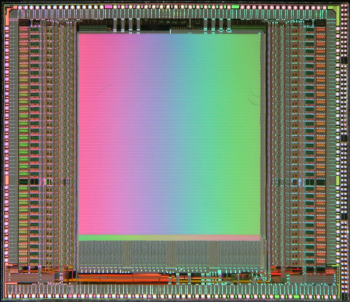

L'ASIC DREAM: 700 000 transistors, 1/2 cm2. Chacun des 64 canaux convertit le signal détecteur, le filtre et mémorise sa forme dans 512 points mémoire analogiques.

STREAM : laboratoire des Systèmes Temps Réel, Electronique d’Acquisition et Microélectronique conçoit et réalise les éléments en électronique analogique, numérique et programmable des instruments de détection utilisés par les expériences des différentes thématiques de l’Institut

Le laboratoire regroupe 14 permanents et 6 non permanents sur l’éventail de métiers suivants : microélectronique analogique et mixte analogique/numérique, support associé pour la caractérisation, bonding de puces et le test de production de circuits intégrés à usage spécifique (ASIC), architecture des systèmes d’acquisition de données, conception de cartes électroniques analogiques et/ou numériques, programmation de micro-logiciel de circuits logiques programmables in-situ (FPGA) et informatique des systèmes temps réel embarqués.

Le laboratoire STREAM travaille en synergie avec les services de physique de l’Institut et les autres laboratoires du Sédi pour apporter des contributions significatives à des expériences scientifiques de tout premier plan.

Le système d’acquisition du trajectographe de l’expérience de physique nucléaire Clas12 est un exemple de cette combinaison de compétences : la puce DREAM, conçue au laboratoire STREAM et basée sur un savoir-faire en micro-électronique analogique bas bruit et sur les mémoires analogiques, est la brique de base des cartes frontale FEU, co-développées avec le Liseta. Ces cartes effectuent la lecture de détecteurs Micromegas cylindriques développés au SEDI. Ce système de lecture, qui comportera au final 20,000 voies, est en cours de livraison et d’installation à Jefferson Lab (USA). Sur la mission spatiale franco-chinoise SVOM, les laboratoires STREAM et Lilas partagent le développement du firmware et du logiciel embarqués à bord de l’Unité de Gestion Technique et Scientifique (UGTS) de ce satellite. Le laboratoire STREAM a par ailleurs conçu et produit les ASICs de vol du télescope grand champ ECLAIRs, élément clef de la charge utile de SVOM. Pour des applications spatiales toujours, l’expertise du laboratoire STREAM en microélectronique bas bruit durcie aux radiations lui a permis de développer et produire en collaboration avec le service d’astrophysique, les micro-gamma camera hybrides « Caliste » pour le satellite Solar Orbiter.

Les autres projets principaux actuels du laboratoire concernent la Phase 1 du programme d’améliorations des expériences du grand collisionneur de hadrons (LHC) au CERN, avec une contribution en micro-électronique aux détecteurs silicium pixellisés monolithiques du Muon Forward Tracker de l’expérience ALICE et la prise en charge de la conception et de la réalisation des quelques 600 cartes frontales « SOLAR » du Bras-Dimuon. Dans l’expérience ATLAS, les laboratoires STREAM et LISETA partagent avec des partenaires américains la responsabilité de la conception et de la production des ~150 cartes de numérisation hautes performances et durcies aux radiations « LTDB ».

Une des activités de R&D du laboratoire concerne la micro-électronique cryogénique et la conception de limandes supraconductrices pour la lecture de matrices de bolomètres infra-rouge ou rayons X pour les applications en astrophysique.

Le laboratoire anticipe également la montée en puissance de la Phase 2 du programme d’améliorations des expériences au LHC en développant des détecteurs pixels CMOS haute tension pour le trajectographe interne d’ATLAS. De même le futur ASIC frontal de la partie centrale du calorimètre électromagnétique de CMS est en cours de conception au laboratoire.

Prototype de la Liquid argon calorimeter Trigger Digitizer Board (LTDB). Cette carte durcie aux radiations est un amplificateur-numériseur 320 voies, 12 bit, 40 MHz à sorties optiques (192 Gbit/s de débit brut total). Le modèle final intégrera plus de 10,000 composants sur un circuit imprimé 24 couches de 41 cm x 50 cm. Cent cinquante unités seront utilisées dans l’expérience ATLAS.