The steps that follow the analogical processing of detector signals are generally performed by digital systems. Today, the production of basic logic functions, data processing and data transfer tasks is essentially based on the use of logic circuits that are programmable in-situ, and on FPGAs (Field Programmable Gate Arrays). Operating these commercial components covers two of DAPNIA’s application fields: embedded systems in harsh environments and very high-speed data acquisition systems.

As part of the Antares project, 350 acquisition boards composed of a processor and an FPGA as well as 60 Ethernet switching boards have been developed and integrated. All boards produced meet the reliability and quality assurance constraints required for embedded systems. These boards constitute the acquisition nodes for the distributed architecture of underwater detectors. Using its experience from the Antares project, DAPNIA is involved in a European underwater detector project KM3Net.

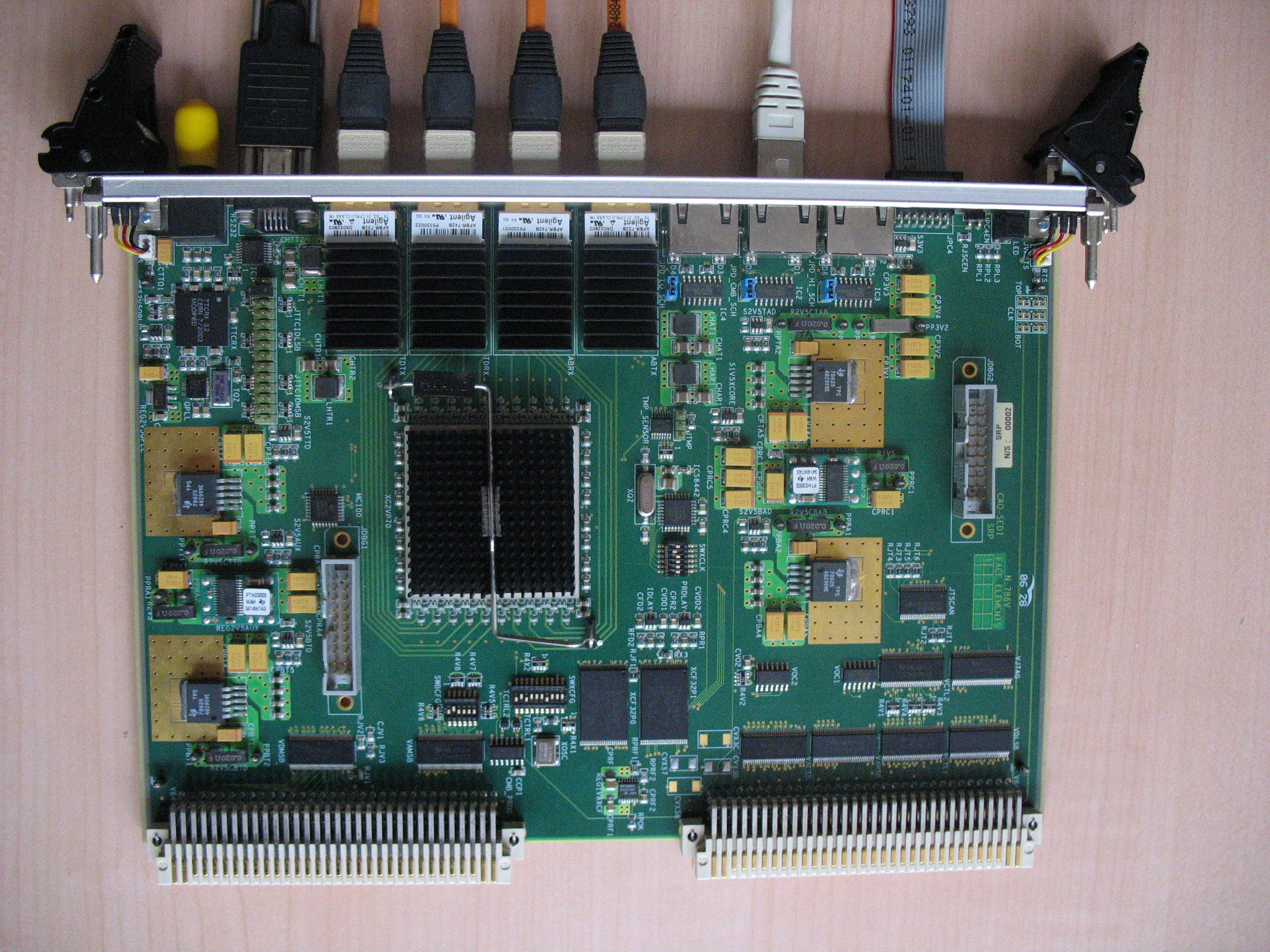

In the field of acquiring and processing data from highly-segmented experimental devices producing a massive data flow, the Selective Read-out Processor (SRP) project is implementing 200 very high-speed optical liaisons (1.6 Gbit/s). This system is used to process data from the CMS experiment’s electromagnetic calorimeter in real-time, using highly-developed design boards: FPGA with several million gates, parallel optic readers, dense and complex printed circuits. An important milestone was reached with the functional validation of this system.

• Innovation for detection systems › Signal processing and real time systems